## 物理屋のための電子回路論 第13回

勝本信吾 東京大学理学部・理学系研究科 (物性研究所)

2017年1月8日

## 7.3 論理ゲートの実装

以上簡単な例で見たように、ICへのカプセル化によって回路図や配線は劇的に簡単になり論理 ICのピン間を回路図通りにつなげば良い、と考えられていた時期があった.このため、自作のディジタル回路では、左の写真のように長いピンを持つ IC ソケットに硬めの配線を巻き付けて結線するワイヤラッピング配線法が盛んに使用されていたこともあり、現在でもシミュレータで十分に拾いきれない問題を調べるため、テスト回路などでは使われている.しかし、すでに述べたように、高いクロック周波数での動作、また前回述べた EMC の観点などから、このような配線法はあまり行われなくなり、自作やテストも FPGA を用いることが多くなった.

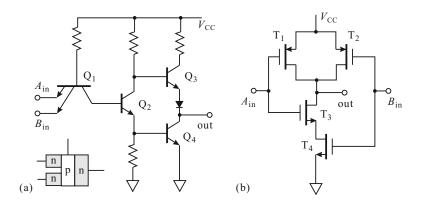

以上は余談であり、本節の目的はこのように「カプセル化」されているディジタル IC 論理ゲートのアナログ的中身について簡単に見ておくことである。これは、カプセル-ブロック化した IC の様々な物理的規定がどのような原因で生じているかを理解するためである。図 7.9 に論理ゲートの回路構成法の代表である、TTL (transistor-transistor logic) と CMOS (complimentary metal-oxide-semicondcutor) による nand ゲートの構成例 (等価回路) を示した、いずれも 4つのトランジスタまたは FET で構成されているが、その仕様のされ方はかなり異なっている。

(a) の TTL 構成では、入力にダブルエミッタトランジスタを用いている. これは挿入図にも示したように 2 つのトランジスタが並列になっているものとして動作を理解することでができる. 従って、 $A_{\rm in}$  または  $B_{\rm in}$  が 0 (L, GND) であれば、トランジスタ  $Q_{\rm 1}$  が ON になって電流が流れ、 $Q_{\rm 2}$  を ON にする.  $Q_{\rm 3}$  と  $Q_{\rm 4}$  はプッシュプル回路を構成しており、 $Q_{\rm 2}$  が ON の時は  $Q_{\rm 3}$  が ON で  $Q_{\rm 4}$  が OFF, $Q_{\rm 2}$  が OFF の時は  $Q_{\rm 3}$  が OFF で  $Q_{\rm 4}$  が ON になるように回路定数が決められている. 以上から、入力が両方 H になった時のみ  $Q_{\rm 1}$  が OFF になって出力が GND 側に振れ、nand動作をすることがわかる. この回路から、TTL では入力レベルとして初段のトランジスタを ON/OFF することが求められること、出力は  $V_{\rm CC}$  から GND まで振れるわけではなく、出力段のプッシュプルトランジスタによる電圧ドロップを考慮しなければならず、また、出力の負荷抵抗によって出力電圧が変化することも理解される.

これに対して、(b) の CMOS 構成は非常に簡潔である。complimentary という名前の通り、必ず p チャネル、n チャネル両方の MOS-FET を使用する。これは、全く同じ入力電圧に対して ON と OFF の逆の動作をするスイッチが使えることを意味し、このような入力に対して自在に  $V_{\rm CC}$  側と GND 側とをつなぎ替えることが可能である。 (b) では、 $A_{\rm in}$ 、 $B_{\rm in}$  の H 信号に対して OFF になる p-MOSFET を  $V_{\rm CC}$  に並列につなぎ、ON になる n-MOSFET を GND に直列接続している。このため、両方が H になった時のみ出力が GND に接続され、それ以外は  $V_{\rm CC}$  に接続されて nand 動作をすることがわかる。 MOS 回路は次段の入力抵抗が非常に高いのが普通であり、これに対して FET の ON 抵抗は無視でき、ON/OFF 電圧の  $V_{\rm CC}$ /GND からのずれは、FET の自己バイアス分で TTL に比べて 大きな出力の振幅が取れることがわかる。もちろん、この素朴な回路では、電源側に接続した並列回路と接地側の直

図 7.9 (a) TTL 構成による nand ゲート内部回路の等価回路例. 挿入図はダブルエミッタトランジスタの層構成模式図. (b) CMOS 構成による nand ゲート内部回路の等価回路例. 内向き矢印 MOS-FET は p チャネル, 外向き矢印は n チャネル. (エンハンストモード)

列回路とが遷移領域で同時に ON となって筒抜けになる危険性があるなど,この周辺に様々な安全回路を設ける必要がある.

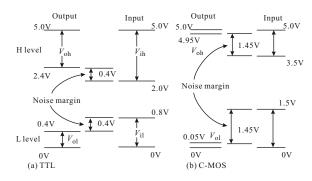

以上から,論理ゲートを動作させるための特徴的な電圧が, $V_{\rm CC}$  を 5V に設定した場合,図 7.10 のようになることが理解される.ただし,特に TTL の場合,適当な負荷や電源の周囲配線をすることが前提となっている.また, $V_{\rm CC}$  を 5V から大きく変更することは,TTL の場合,通常の半導体物質パラメタから困難であることも理解されるであろう.

図 7.10 標準論理ゲート動作の電圧ダイアグラム. (a) TTL, (b) C-MOS

歴史的にみると、IC 化され論理ゲートして盛んに使用され始めたのは TTL が先であり、圧倒的な利用範囲を持っていたため論理信号の H、L が 5V、0V というのが標準となった。初期の頃の CMOS IC は、動作のためにむしろ高い電源電圧を必要とし、TTL 回路と接続のためにはレベル変換回路を用意したりした。また、やはり初期は CMOSの動作速度は TTL を改良した LS 型、ALS 型に及ばず、PC の周辺回路等、ほとんど TTL で組まれていた。しかし、クロック周波数が高くなり LSI の集積度が高くなるにつれて、素子間の距離をできるだけ短くすることが非常に重要になり、ゲートあたりの素子数が少なく、電流がゲートの帯電/放電時のもの程度で消費電力が極めて小さい CMOS が次第に有利となった。素子特性も単ゲート化によってむしろ改善され 5V より低い電圧でも十分動作するようになり速度も向上した。3.3V や 2.5V を H レベルとする回路も増え、最近では京などのスーパーコンピュータの CPU も CMOS となり、現在のところ論理ゲートの世界は CMOS に完全支配されてしまったように見える。

ただし、CMOS も含めて論理演算そのものが現在様々な物理的壁に当たっており、並列計算などのソフトウェア手法で全体としての行き詰まりを回避しているのが現状であるから、ハードウェア側にも何か大きなフレークスルーがある可能性はある.

## 7.4 論理演算の回路化と簡単化

アナログ回路が力学系など、物理系の表現と見ることができたのに対し、ディジタル演算回路は、論理式の具体的表現と見ることができる。従って、論理式が演算を代数的に行うことで簡単化されれば、回路を簡単化することになる。その代表的方法を説明する。また、順序回路は「状態」概念が入ってくるため、これに対応する論理式側の取り扱い概念が必要となる。その1つ(ツール)であるダイアグラムを紹介する。

### 7.4.1 カルノ一図

#### A, Bを論理値として論理式

$$Y = A \cdot B + A \cdot \overline{B} + \overline{A} \cdot B \tag{7.1}$$

を考える. · は and, + は or を表す. 論理値においては, A+A=A であったことから, 右辺に  $A\cdot B$  を加えて変形すると

$$Y = A \cdot B + A \cdot B + A \cdot \overline{B} + \overline{A} \cdot B$$

=  $A \cdot (B + \overline{B}) + B \cdot (A + \overline{A}) = A + B$  (7.2)

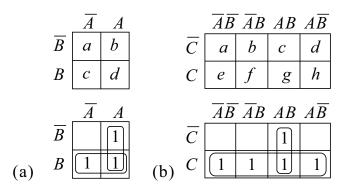

となり、単なる or 演算であったことがわかる.  $A\cdot B$  を加えるような論理演算は式だけでは思いつきにくく、真理値表を睨むなどの非機械的手法がむしろ有効である. これを比較的機械的に行う手法がカルノー図 (Karnaugh map) の手法である.

図 7.11 カルノー図の例. (a) 2 論理変数に対するカルノー図. 下は or 論理演算の場合. (b) 3 論理変数に対するカルノー図. 下は,  $\overline{A} \cdot \overline{B} \cdot C + \overline{A} \cdot B \cdot C + A \cdot B \cdot \overline{C}$  の場合.

カルノー図とは、ある論理式に対し図 7.11 のようにそれを構成する論理変数のすべての場合を 2 次元に並べて書いたものである。マスの中には出力が 1 (T) となる場合のところに 1 を入れるようにする。3 変数の場合,2 変数ずつをまとめて書くと図 7.11(b) のように 2 次元にしておくことができる。この時,隣のコラムを作る際に 2 変数同時に否定を取ることはせず,1 つづつ取って場合を潰すことが必要である。このように論理変数の数が増加すると次第に図が描きにくくなる。

式 (7.1) の場合をカルノー図に描くと図 7.11(a) の下の図になる.隣接する「1」を で括ると,2 つの括りができることがわかる.すなわち,このカルノー図が表す論理式は,この2 つの「括り」が表す論理式の or を取ったものである.

$$Y = A \cdot \overline{B} + A \cdot B + \overline{A} \cdot B + A \cdot B = A + B \tag{7.3}$$

と, 当然 (7.2) の結果が得られる. 図 7.11(b) の下の図は

$$Y = \overline{A} \cdot \overline{B} \cdot C + \overline{A} \cdot B \cdot C + A \cdot B \cdot C + A \cdot \overline{B} \cdot C + A \cdot B \cdot \overline{C} + A \cdot B \cdot C = A \cdot B + C \tag{7.4}$$

である.

以上見てわかるように、カルノー図による簡単化の原理は

$$A \cdot B + A \cdot \overline{B} = A \tag{7.5}$$

という簡単なものであるが、図 7.11 のように 2 次元に並べて隣接する 1 を括ることでこのようにして消せるペアを組織的に見つけられる、というところが利点である。なお、「隣接する 1」を探す際、行や列の端同士は隣接している、と見なければならないので注意が必要である。例えば、図 7.11(b) の上の図で a と d や e と h は隣接している。

## 7.4.2 クワイン・マクラスキー法

この簡単化を更に機械的手続きにすることを考える.このためには、最初に与えられた論理式の形は、簡単化を標準化するためにはむしろ障害になることが多く、カルノー図のように一旦真理値表で表してしまい、そこから一定の標準的手続きにより論理式に戻すことにする.

論理式  $Y=f(A_1,A_2,\cdots,A_n)$  を考える. 真理値 0, 1 に対して、各論理変数を与える関数  $g_i$  を

$$g_i(0) = \overline{A}_i, \qquad g_i(1) = A_i \tag{7.6}$$

と定義する。各変数またはその否定をすべて1つずつ含む論理式(項)を標準項(canonical term)という。うち、論理和 + を区切りとして分解される「項」の数が最も少ないものを最小項と呼ぶが、最小項は当然項数1個であるから、結局最小項とは、 $\prod_{i=1}^n g_i(a_i)$ で表される。 $a_i=0$  または1で、 $\prod$  は論理積を表す。Y を真理値表で表す時、ある1行の入力項は0または1のn 個の真理値列であるから、これを $\{a_i\}$  と見ると、真理値表の各行に1個の最小項が対応することがわかる。そこで、Y=1 を与える $\{a_i\}$  をすべてリストアップして指数j を付け、行列の形で $\{a_{ij}\}$  と表すと、Y の論理式としてこれらで指定される最小項をすべて論理加算したもの

$$Y = \sum_{i} \prod_{i=1}^{n} g_i(a_{ij}) \tag{7.7}$$

を考えることができる. このように最小項の論理和での論理値の表現を**主加法標準展開** (principal disjunctive canonical expansion) と呼ぶ.

主加法標準展開から (7.5) を使い冗長項を圧縮していく. この時、最小項を作るために考えた  $\{a_i\}$  を並べたものを 2 進数として取り扱う方法を特にクワイン・マクラスキー法 (Quine-McCluskey algorithm) と呼んでいる. これら 最小項を表す 2 進数を、その中に出てくる「1」の個数で分類する. 2 進数表示での (7.5) は、0 と 1 とを取るある桁 以外は同じ 2 進数の間でこの桁を消去する式であるから、圧縮はこの分類で 1 つだけ異なるグループ間で行われる. 消去した桁は (r) グースコア) として並べることで第 1 次圧縮リストができる。再度 1 の個数で分類、圧縮を可能 な限り繰り返す.

こうして簡単化された論理式について、各項 (「主項」と呼ぶ)を行指数とし、元の主加法標準展開に含まれる最小項を列指数とする (反対でも良い) 表 (主項図)を作る。最小項の中に何らかの形で主項が含まれている欄に印をつける (○とする)。例えば、主項が  $_-$ 11 であれば、0011、0111、1011、1111 の 4 つがそれに当たる。論理的には「これらの最小項を主項が包含する」ことになる。この表をまず縦に見て、○が 1 回だけ現れる最小項の○を◎に変更する。次に横に見て、◎がついた主項 (必須項)の行に◎になっていない○があればこれをすべて◎に変更する。最後に○しか付いていない主項が省略候補である。すべての最小項をカバーするように必要な主項があれば残し、後を省略することで簡単化が終了する。

図 7.12 状態遷移図. (a) 概念図. (b) 4 進カウンタ.

#### 7.4.3 状態遷移図

順序回路を設計する際に、ダイアグラムとして助けになるのが**状態遷移図** (state transition diagram) である. これは図 7.12(a) のように、入力 a に対して回路の状態が  $q_0$  から  $q_1$  へと遷移し、b が出力されるということを表している.

これを使って、7.2.4 節で見たカウンタ回路の設計 手順を追ってみる。簡単のため、2 ビット (4 進) カウンタとする。カウント入力が入る度に状態が変化し、初期状態から 4 つ目のカウント入力で 1 を出力して初期状態に戻るから、状態は全部で $q_1, \cdots, q_4$  の 4 つで

ある. 図 7.12(b) のようにこの 4 つの状態を並べて書き,入力 x=0 の場合は状態が変化せず出力も 0 なので,0/0 でループを描いて元の状態に戻り,1 に対しては状態が 1 シフトし, $q_4 \rightarrow q_1$  の初期値に戻るときのみ 1 が出力されるので 1/1,それ以外は 1/0 となる,ということで,図 7.12(b) のような状態遷移図が描かれる.

2 ビットであるから T-FF を 2 個使用して実現することにする。これら 2 個の出力を、状態  $q_n$  に対してそれぞれ、 $Q_n^{(1)}$ 、 $Q_n^{(2)}$  と書く。n は 4 進で回る、すなわち 4+1=1 とする。状態遷移表をカルノ一図の形にするため、 $Q_{n+1}^{(1)}$  とに分けて描くと次のようになる。ただし、最初にビットが上がる方を (2) の T-FF としている。 $(Q_{n+1}^{(i)}$  を決めるための論理変数が、x、 $Q_n^{(1)}$ 、 $Q_n^{(2)}$  の 3 つ存在するため、図 7.11(b) を縦にした図になっている。

カルノ一図であるから、 で隣接する1を囲い、簡単化により次のような漸化式を得る.

$$Q_{n+1}^{(1)} = \overline{x} \cdot Q_n^{(1)} + Q_n^{(1)} \cdot \overline{Q}_n^{(2)} + x \cdot \overline{Q}_n^{(1)} Q_n^{(2)}, \tag{7.8a}$$

$$Q_{n+1}^{(2)} = \overline{x} \cdot Q_n^{(2)} + x \cdot \overline{Q}_n^{(2)}. \tag{7.8b}$$

また、一般に FF については、入力 x で表される論理式  $\alpha$ 、 $\beta$  を用いて

$$Q_{n+1} = \alpha Q_n + \beta \overline{Q}_n \tag{7.9}$$

という、**特性方程式** (characteristic equation) と呼ばれる式が成立する. 実際、図 6.5(b) の T-FF の真理値表から、 $\alpha = \overline{T}$ 、 $\beta = T$  として、(7.9) が成り立っていることがわかる. T-FF の (1)、(2) に対応して  $\alpha_{1,2}$ 、 $\beta_{1,2}$  と添字をつけると、(7.8a)、(7.8b) より、

$$\alpha_1 = \overline{x} + \overline{Q}_n^{(2)} = \overline{x \cdot Q_n^{(2)}}, \qquad \beta_1 = x \cdot Q_n^{(2)},$$

(7.10a)

$$\alpha_2 = \overline{x}, \qquad \beta_2 = x \tag{7.10b}$$

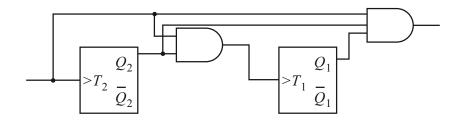

である. 以上から, 図 7.13 の回路図がほぼ自動的に描かれる.

# 7.5 A-D/D-A コンバータ

アナログ信号をディジタル信号に変換する,あるいはその逆の動作をする回路は,物理実験では極めて重要である.D-A/A-D 変換回路技術は,音響・映像技術にディジタル技術が入り込んで以来飛躍的に発展した.素子性能の向上による性能向上ばかりでなく,信号形式,回路方式の改革によって古い電子回路の教科書はみな書き換えなければならないほどの進歩が積み重ねらている.ただし,A-D/D-A 技術に関しては,CCD 技術,画素式ディスプレイの発達によりまず映像系からアナログ回路がほとんどなくなり,音響においても D 級アンプやスピーカーのデジタ

図 7.13 設計した 4 進 (2 ビット) カウンタ ル駆動によりアナログ回路はディジタルのカプセルの向うの存在となりつつあることから、今後はこれまでのような 急速な進展はないかもしれない.

「変換回路」と言っても、一方 (アナログ) が物理量であるのに対して他方 (ディジタル) は、人間がこれを記述するために考えた記号であるから、「変換」のためには極めて様々なアイデアが存在しうる。これらは、変換形式に従い、外部クロックが必要になるなどの若干の使用法の違いはあるものの、A-D コンバータ (ADC)、D-A コンバータ (DAC) として LSI 化されてカプセル的に使用することが可能で、内部形式を知らなくても使えてしまう。それでも、どのようにして変換しているのか知っておくことは、電子回路の応用例としても悪くはない。代表的な回路形式を紹介しておこう。

## 7.5.1 ディジタル-アナログ変換

まず、ディジタルからアナログへの変換を考えよう.

#### 抵抗ストリング型、ラダー型

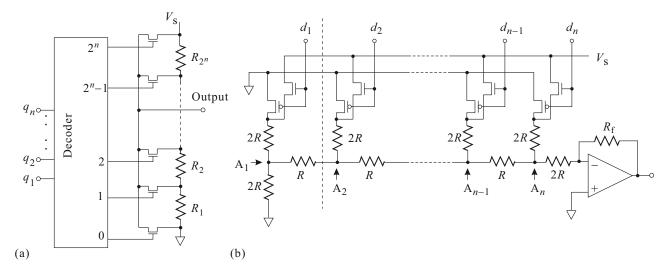

図 7.14 抵抗ネットワークを用いた D-A コンバータの等価回路図. (a) 抵抗ストリング型. (b) 抵抗ラダー型. FET スイッチは、ゲートに $\bigcirc$ がついていないものが n チャネルで H 入力に対して ON、反転記号である $\bigcirc$ が付いているものが p チャネルで H 入力に対して OFF となる.

抵抗ネットワークを使用するものの内,図 7.14(a) に示した抵抗ストリング型は,余り現実性はないが,コンセプトとしては最も単純なものである。n ビットのデジタルデータは  $2^n$  の分解能を持っている。そこで,回路は標準電圧  $V_S$  を持っているとし,これを, $2^n$  個の同一抵抗値 R を持つ抵抗を直列につないだ回路に印可する (他端はグラウンド)。グラウンドから順番に抵抗に  $1,\cdots,2^n$  の番号を付けると,i 番目と i+1 番目の抵抗の間の配線部の電位は, $i\times V_S/2^n$  となり,出力へは図のように,MOS スイッチを用いて接続する。受電部の入力インピダンスを十分高くし,バイアス電流を抵抗ストリングに流す電流に比べて十分に低く取ることで  $i\times V_S/2^n$  をそのまま出力できる。

この方法は現実問題として、8 ビットでも 256 個の高精度抵抗と MOS スイッチを結線する必要があり、デコーダーも同じだけの数の出力を要するなど、使いにくいものである.

これに対して実際にもよく使用されるのが図 7.14(b) の抵抗ラダー型 DA 変換である. n-1 個の抵抗値 R の抵抗  $ext{th}$  と  $ext{th}$   $ext{th}$  2 個の値  $ext{th}$  2 個の抵抗を用意し、 $ext{th}$   $ext{th}$   $ext{th}$  2 個の抵抗を介して  $ext{th}$  の抵抗を直列にした各端点に接続する. 最低ビットラインの端点は  $ext{th}$   $ext{th}$  e

OP アンプの項で学んだように,- 入力端子は仮想接地されているので,ここでは右端の 2R もやはり接地されているものとして  $A_n$  点の電位を考える.今,k ビット目が 1(H) で他はすべて 0(L) が入力されたとする. $A_n$  点から右および上方の接地側を見ると 2R の抵抗が 2 個並列になっており,合成抵抗 R で接地されている.従ってその左の

$A_{n-1}$  点から右方向の  $A_n$  点を通る経路の接地までの合成抵抗はやはり 2R で  $A_n$  点と状況が全く同じであることがわかる.これが, $A_{k+1}$  点まで続く. $A_{k-1}$  点より左側を見ても,全く同じ状況である.従って  $A_k$  点は,左右に 2R で接地され, $V_{\rm S}$  より 2R を通して接続されていることがわかる.結局流れる全電流は  $V_{\rm S}/3R$ ,片方の分岐に流れるのはその 1/2 である.以下,分岐ごとに 1/2 になるので,最終的に OP アンプ方向へ流れ出す電流は

$$J_{\text{out}}(\begin{array}{ccc} 0 \cdots 0 & 1 & 0 \cdots 0 \\ n & k & 1 \end{array}) = \frac{V_{\text{S}}}{3R} \left(\frac{1}{2}\right)^{n-k+1} = \frac{V_{\text{S}}}{6 \cdot 2^n R} 2^k$$

となる.  $J_{\text{out}}$  の引数は、入力を 2 進数で表したものになっている. 従って、入力  $\{d_i\}$   $\{d_i\}$   $\{d_i\}$   $\{d_i\}$   $\{d_i\}$   $\{d_i\}$   $\{d_i\}$  があった時の OP アンプ出力は、重ね合わせの定理  $\{2.5\ \hat{\mathbf{m}}\}$  を用いて、

$$V_{\text{out}}(\{d_i\}) = -\frac{1}{3 \cdot 2^n} \frac{R_f}{2R} V_S \sum_{k=1}^n 2^k d_k$$

(7.11)

となって、AD 変換がされている事がわかる. ストリング型に比べて必要抵抗は圧倒的に少なく、デコーダなども必要としない. 実際多用される形式である.

この他,受動素子ネットワークを用いるものとしては,容量アレイ型などがある.

#### 電流加算型

原理的にはたいへん簡単な変換法であり、レポート問題として考えて もらう予定.

#### 容量アレイ型

これも簡単なので、レポート問題として考えてもらう予定である.

### パルス幅変調型

パルス幅変調 (pulse width modulation, PWM) は、どちらかと言う とアナログ信号を PWM 信号にしてパワートランジスタをスイッチす

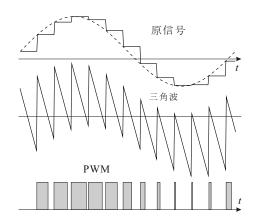

図 7.15 パルス幅変調法の一例.

ることで電力増幅し、ローパスフィルターでアナログ信号に戻す、アナログ電力増幅に用いることが多い.が、無論、速くて正確なクロック信号とカウンタを用いてディジタル的に PWM 信号を作り出すことができ、これをローパスフィルターに通すことで DA 変換ができる.

原理は以上で終了,という位簡単明瞭である.逆に PWM 信号を作り出す方法の一例を図 7.15 に示した.クロックに同期したのこぎり三角波を作り出し,原信号でベースラインをシフトさせる.これをコンパレーターに入れてこの変調三角波が閾値電圧を超えた領域だけ H 信号を出すようにすることで, PWM 信号が得られる.

### 7.5.2 アナログ-ディジタル変換

#### 逐次比較型

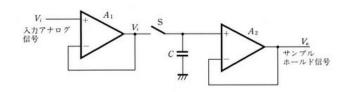

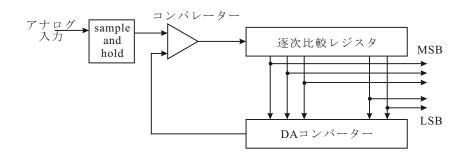

この方式では標本回路 (sample and hold circuit) により入力電圧を固定しておき (これは、他の多くの方式でも用いられる), DA 変換によって既知電圧を作り出し、これとホールドした電圧とが一致するかどうかを調べることでディジタルデータに変換する. 様々な意味での「既知電圧」を次々とホールド電圧と比較することから**逐次比較** (successive approximation) 型と呼ばれている.

サンプルアンドホールド回路 (AD 変換回路ではトラックアンドホールドと呼ばれることもある)にも多くの形式があるが、左図に挙げるものが最も簡単である。信号によってキャパシタにチャージし、これをOP アンプにより孤立状態にして維持する。新しくサ

図 7.16 逐次比較型 AD コンバー ターのブロックダイアグラム

ンプルする際には、放電するのが一般的であるが、信号時間変化が緩やかでかつ低出力抵抗である場合は、帯電状態で接続することも考えられる.

2 進数に変換することから,逐次比較は高いビットから,数値計算でいう 2 分法によって行うのが一般的である.最初に最高ビットのみを立てた参照電圧を DAC により用意し,コンパレーターで比較する.コンパレーターもまた,OP アンプを開ループ (可能な限り大きな開ループゲインを持たせる) で使用するのが精度的に有利である.参照電圧がサンプルより大きければ 0,小さければ 1 が立つ.このディジタル信号の次のビットを立てたものを DAC に入れて次の参照電圧を作る.以下最終ビットまで繰り返すことでディジタル変換が完了する.

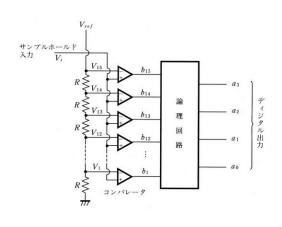

#### フラッシュ型

逐次比較型は1ビットごとに変換していくので変換回路は1回路で済むが、多ビットの AD 変換を行う場合にはビット分だけのサイクルを繰り返す必要があり時間がかかるようになる. これに対して、多数のコンパレーターを並べて一気に AD 変換を行おうというのがフラッシュ型 ADC である. 左図のように、抵抗ストリング型 DAC のちょうど逆のような形式である.

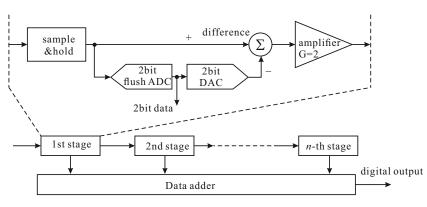

#### パイプライン型

フラッシュ型は逐次比較型に比べて圧倒的な速度を持っているが、当然ながら分解能分の分割抵抗とコンパレーターという消費リソースも巨大となる。また、精度限界はコンパレーターの開ループゲイン A で決まることが多い。例えば、A が 100dB だと

すると、入力  $10\mu V$  で出力は 1V になり、ディジタル回路が TTL レベルで動作しているとすると、しきい値電圧  $V_{\rm th}$  には到達しない。 さりとて、アナログアンプで例えば 10 倍に増幅して入力しようとすると、アンプの出力、あるいはコンパレーターの入力の飽和値によってアナログ電圧の大きさが制限されてしまう。

図 7.17 2 ビット単位パイプライン型 ADC のブロック図

このような欠点を、速度を若干犠牲にしながらカバーする方式が幾つか使われており、パイプライン型はその1つである。図 7.17 はそのブロック図 (後述)で、数ビットをまとめてフラッシュ型で AD 変換し、残った信号を増幅器で増幅しながら次のサイクルを行うようになっている。フラッシュ型と逐次比較型の間の子のような形式である。

#### 積分型

逆に時間はかかるができるだけ少

ない部品リソースで A D変換を行おうというのが積分型 ADC で、積分回路に定電流を流して時間に対してリニア に増加する電圧を作り出し、入力電圧とコンパレーターで比較する。増加電圧が下端からスタートする際にディジタ

ルカウンターをスタートし、増加電圧が入力電圧をクロスしてコンパレーターが ON になった時点でストップする. カウンター出力により AD 変換ができる. 積分回路とコンパレーターの OP アンプと積分用のキャパシタで精度が ほぼ決まり (カウンターの桁数を出すのは比較的容易)、安価に AD 変換を構成できるため、パネルメーター (機器の 表面に沢山はめ込んで、様々なパラメーターをモニターできるようにするもの) などに良く使用されている.

#### デルタシグマ型

オーバーサンプリング型 と呼ばれる ADC の代表的な形式である. 1 ビット (従ってコンパレーター 1 個のみ) の 超低分解能 ACD を用いフィードバックを使ったデルタシグマ変換により高精度ディジタル信号に変換する. 詳細は 後述.

## 7.5.3 情報の符号化

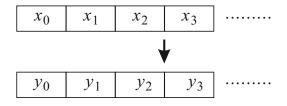

「ディジタル信号序論」で述べたように、パルス振幅変調 PAM でパルス高を離散化すれば、ディジタル信号になる。それをそのまま変調の形にしたのが**パルス符号変調** (pulse code modulation, PCM) である。PCM データは、クロックに合わせて何ビットかのデータを伝送するもので、少ない伝送チャネルで送る場合は、時系列信号にしてシリアル伝送する。復調する必要がある場合は、パラレルデータに変えて DAC によりアナログ信号にする。

この直接的な PCM 法に対して、様々な変形がある。ディジタル信号は符号化されたものであるため、急激な信号値変化もデータ上は表現できるが、アナログ信号は、特にそれに含まれている周波数成分の上限で表現できるよりも大きな変化は生じない。そこで、値そのものではなく前の信号値との差分を抽出して伝送することも考えられる。これを差分 PCM (differential PCM, DPCM) 方式と呼び、予測符号化方式の一種である。DPCM は一般に PCM より小さなビットレートで同精度の信号を伝送することができる。「予測」という文字がついているのは、実際には単なる差分ではなく、最も単純な前値予測方式であっても予測係数がついて、受信データ  $\{x_i\}$  に対する予測値は  $x_i'=ax_{i-1}$  で与えられ、送付データは差分  $\epsilon_i=x_i-ax_i'$  である。

また、PCM でない符号化形式 (時間領域で変換してから符号化するもの) など、符号化にも沢山の形式があるが、とても踏み込む余地がないので本講義ではここまでとする.

## 7.6 ディジタルフィルター

一旦ディジタルに落とした信号は、回路中で数値として扱うことができるので非常に自由度が高く、安定な処理が可能である。このような「処理」の内、ディジタル信号からディジタル信号への変換処理を $\mathbf{7}$  の内、ディジタル信号からディジタル信号への変換処理を $\mathbf{7}$  の内、作用と呼ぶ。ディジタル信号処理 (digital signal processing, DSP) も極めて巨大な分野であり、講義の 1 回程度ではほとんど「舐めてみる」程度のことしかできないが、ディジタルフィルターの初歩について考え、入り口を経験することにしよう。なお、この  $\mathbf{DSP}$  という略語は「ディジタル信号処理」という意味、および「ディジタル信号プロセッサー」 (digital signal processor) の両方に用いられ、混用されている。

ディジタルフィルターは物理的に行っていることはアナログフィルターとは全くと言って良い程異なっているが、 応答関数の形に書くと、類似の舞台の上で考えることができる対象であることがわかる。ディジタルフィルターは、 アナログフィルターがスマートに滑らかに行っていたことをゴツゴツと各段階計算で押し切っているので必要な回路 リソースは桁違い以上に大きいが、特性が部品特性に制約されず設計に対する忠実度が高く、自由な設計が可能であ り、何より、制御信号などによって容易に特性を変化させることができる。

### 7.6.1 ブロック・ダイアグラム

ディジタルフィルターの働きを簡単にまとめると、右図のように見るのが 1 つの考え方であろう。 すなわち、時系列で並んだ数列  $\{x_i\}=(x_0,x_1,\cdots)$  に対して、別の数列  $\{y_i\}=(y_0,y_1,\cdots)$ を得るプロセスである。ここで、数列値  $y_n$  は、 $x_n$  およびこれよ

りも以前のk個の $x_i$ の値によって決定されるとすると、k+1変数の関数Fを使って

$$y_n = F(x_{n-k}, x_{n-k+1}, \cdots, x_n)$$

(7.12)

と書けることになる.

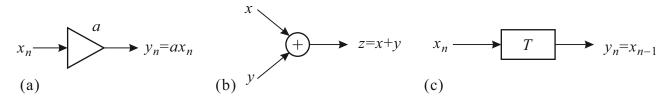

図 7.18 ディジタルフィルター用ブロックダイアグラムに使われる,「基本ブロック」. (a) 定数倍回路. (b) 加 算回路. (c) 遅延回路 (シフトレジスタ).

図 7.19 式 (7.13) のダイアグラム化.

F として現実には数列要素間および定数との 間の加減乗除がはいることがほとんどである. これまでも回路を機能のまとまりで記述した ブロック・ダイアグラム (block diagram) で表 すことを良く行ってきたが, ディジタルフィル ターの F は、簡単な要素を使ってブロック・ダ イアグラムで表すことが良く行われる. その基 本要素とは図 7.18 の 3 つであり, (a) はディジ

タル回路のバッファの形をしているが、記入されている数倍だけする、定数倍回路、である. (b) は信号の和を取る 加算回路である. (c) は、信号を時間領域で1単位だけ遅らせる遅延回路である.

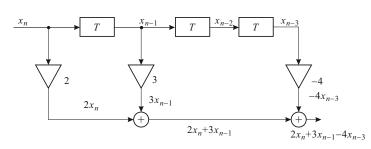

例として

$$y_n = 2x_n + 3x_{n-1} - 4x_{n-3} (7.13)$$

をダイアグラム化すると前頁の図のようになる.

## 7.6.2 z 変換空間表示

ディジタルの線形応答回路においてもアナログ回路同様、z変換空間において伝達関数を使って応答関係を表すこ とができることを示した. そこで、ディジタルフィルターも (片側) z 変換空間で表すことを考える.

ここではやはり例として (7.13) を考える. 今の場合,フィルターの入出力の z 変換は定義 (6.83) より,

$$X(z) = \sum_{n=0}^{\infty} x_n z^{-n}, \quad Y(z) = \sum_{n=0}^{\infty} y_n z^{-n}$$

(7.14)

である. ここで、表 5.2 に示した片側 z 変換の性質を思い出すと、線形性より加 算や定数倍はそのまま記述することができ、周期 $\tau$ のk回文の遅延は時間移動 で $z^{-k}$ をかければ良いことがわかる.以上より, z変換空間では

$$Y(z) = 2X(z) + 3z^{-1}X(z) - 4z^{-3}X(z) = (2 + 3z^{-1} - 4z^{-3})X(z)$$

(7.15)

で表されることがわかる. これより、伝達関数を H(z) とすると、(6.89) より

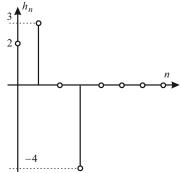

$$H(z) = 2 + 3z^{-1} - 4z^{-3} (7.16)$$

となることがわかる.

伝達関数は t=0 でインパルス入力があった時の応答の z 変換であるから、これより、このディジタルフィルターにインパルス入力があると、前ページの図のような応答があることになる。一般にフィルターの関数 F(7.12) が、

$$F(x_{n-k}, x_{n-k+1}, \cdots, x_n) = \sum_{j=0}^{k} a_j x_{n-j}$$

(7.17)

のようにかける場合, 伝達関数は

$$H(z) = \sum_{j=0}^{k} a_i z^{-j} \tag{7.18}$$

となる.

### 7.6.3 ブロックダイアグラムと伝達関数

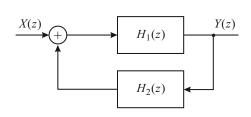

z変換空間内でもブロックダイアグラムを考えることができる. この際,伝達関数をブロックで表してしまうのが簡単である. 左図のように,2つの伝達関数  $H_1(z)$  と  $H_2(z)$  とを使って,フィードバック構造をつくるブロックダイアグラムを考えてみる. X(z) から + 演算を経て  $H_1$  へ入力される関数を W(z) と置くと,

$$Y(z) = H_1(z)W(z) = H_1(z)(X(z) + H_2(z)Y(z)),$$

$$\therefore Y(z) = \frac{H_1(z)}{1 - H_1(z)H_2(z)}X(z).$$

すなわち,全体の伝達関数は

$$H(z) = \frac{H_1(z)}{1 - H_1(z)H_2(z)} \tag{7.19}$$

これは、むろん、アナログ回路の場合の(4.3)式に対応するもので、フィードバック回路の場合、一般に

$$(全体の伝達関数) = \frac{(直接部分の伝達ゲイン)}{1 - (フィードバック部分の伝達ゲイン)}$$

(7.20)

となることを示している. ここで、フィードバックをかけると、式 (7.12) の引数が形式上無限に続くことになることに注意しよう.

# 付録 K: A-D/D-A コンバータ選択・使用上の注意

現在の物理実験家が自ら A-D/D-A 回路を設計製作することはまず考えられないが,集積回路の形で用いる可能性はある.ディジタルオーディオの発展に伴って驚異的な多ビットの DAC などが二束三文で売られるようになり,これらを上手に使用することで高速/高精度の実験測定系が安価・低労力で得られる可能性がある一方,絶対精度等には注意が必要である.

現在オーディオ用に 24 ビットの DA 変換 IC は極めて安価に手に入る. AD 変換も同様であり、中には 32 ビットのような高いビット数を持つものもある. これらはほとんど  $\Delta$ - $\Sigma$ 型の AD 変換器を用いており、相対精度が非常に高くて便利である. が、絶対精度はあまり当てにできないので、計測に用いる場合は精密機器による較正が必要である.

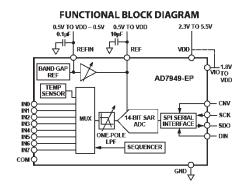

実際に ADC/DAC を選択する場合, データシートをきちんと見る必要がある. まず, どのような回路が使用されているのか把握し, トラブルが生じた際に備える (回路形式が原因の可能性がある). これには, ブロック図を見ておけば十分で, データシートには大抵簡単なブロック

図が掲載してある。左図は AD7949 の場合であり、中に MUX と書かれた 8 チャンネルのマルチプレクサ (入力チャンネル切替器) が入っており、ボード線図で「極」が 1 つだけある低域通過フィルター (LPF) が入れられていることがわかる。その先は「14bit SAR ADC」につながっていて、この IC が 14 ビットの抵抗逐次比較型 (successive approximation resistor) の ADC であることがわかる。

次に見なければならないのが specification table で、面倒でも定格電圧やノイズ、不確定性の最悪値などをチェックし、実験の用途に耐えるものかどうかを調べておく必要がある.

## AD7949-EP

### **SPECIFICATIONS**

$VDD = 2.3~V~to~5.5~V, VIO = 1.8~V~to~VDD, V_{REF} = VDD, all~specifications - 55~^{\circ}C~to + 125~^{\circ}C, unless~otherwise~noted.$

| Ta |  |  |

|----|--|--|

|    |  |  |

| Parameter                    | Conditions/Comments                        | Min                  | Тур                 | Max                  | Uni  |

|------------------------------|--------------------------------------------|----------------------|---------------------|----------------------|------|

| RESOLUTION                   |                                            | 14                   |                     |                      | Bits |

| ANALOG INPUT                 |                                            |                      | *                   | *.                   |      |

| Voltage Range                | Unipolar mode                              | 0                    |                     | $+V_{REF}$           | V    |

|                              | Bipolar mode                               | -V <sub>REF</sub> /2 |                     | +V <sub>REF</sub> /2 |      |

| Absolute Input Voltage       | Positive input, unipolar and bipolar modes | -0.1                 |                     | $V_{REF} + 0.1$      | V    |

|                              | Negative or COM input, unipolar mode       | -0.1                 |                     | +0.1                 |      |

|                              | Negative or COM input, bipolar mode        | $V_{REF}/2 - 0.1$    | V <sub>REF</sub> /2 | $V_{REF}/2 + 0.1$    |      |

| Analog Input CMRR            | f <sub>IN</sub> = 250 kHz                  | 9000000              | 68                  |                      | dB   |

| Leakage Current at 25°C      | Acquisition phase                          |                      | 1                   |                      | nA   |

| Input Impedance <sup>1</sup> |                                            |                      |                     |                      |      |

| THROUGHPUT                   |                                            |                      |                     |                      |      |

| Conversion Rate              |                                            |                      |                     |                      |      |

| Full Bandwidth <sup>2</sup>  | VDD = 4.5 V to 5.5 V                       | 0                    |                     | 250                  | kSP: |

|                              | VDD = 2.3 V to 4.5 V                       | 0                    |                     | 200                  | kSP  |

| 1/4 Bandwidth <sup>2</sup>   | VDD = 4.5 V to 5.5 V                       | 0                    |                     | 62.5                 | kSP: |

|                              | VDD = 2.3 V to 4.5 V                       | 0                    |                     | 50                   | kSP: |

| Transient Response           | Full-scale step, full bandwidth            | 10.0                 |                     | 1.8                  | μs   |

|                              | Full-scale step, ¼ bandwidth               |                      |                     | 14.5                 | μs   |

| ACCURACY                     |                                            |                      |                     |                      |      |

| No Missing Codes             |                                            | 14                   |                     |                      | Bits |

| Integral Linearity Error     |                                            | -1                   | ±0.5                | +1                   | LSB  |

| Differential Linearity Error |                                            | -1                   | ±0.25               | +1                   | LSB  |

図 K.1 AD7949  $\mathcal O$  specification table  $\mathcal O$ 一部

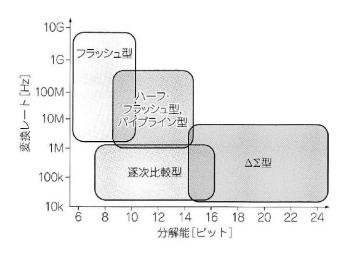

最後に、A-D 変換方式と分解能、変換速度の「分布図」をあげておく.

図 K.2 A-D 変換器の回路方式による,分解能,変 換速度に対する分布図.