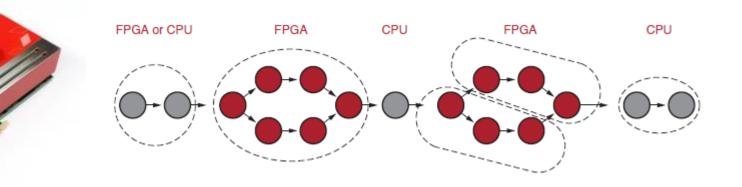

# 電子回路論第14回 Electric Circuits for Physicists #14

東京大学理学部 ・理学系研究科 物性研究所 勝本信吾

Google

Shingo Katsumoto

# Outline

PLD, FPGA Hardware technique

Hardware description language (HDL)

Neural network and FPGA

From https://www.xilinx.com/applications/megatrends/machine-learning.htm

# 7.8 Circuit realization with Hardware Description Language (HDL)

PLD/FPGA with HDL

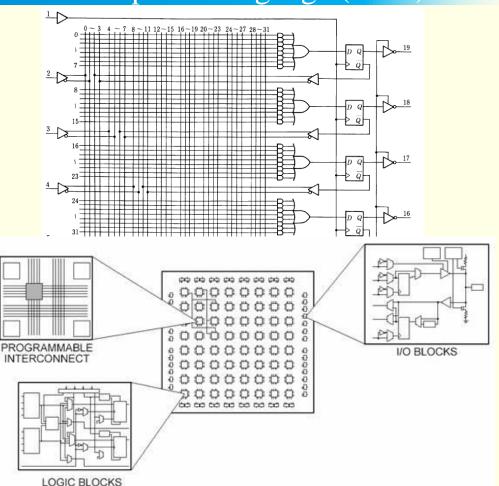

Example of programmable logic device (PLD) circuit

Example of field-programmable gate array (FPGA) circuit

$FPGA \in PLD$

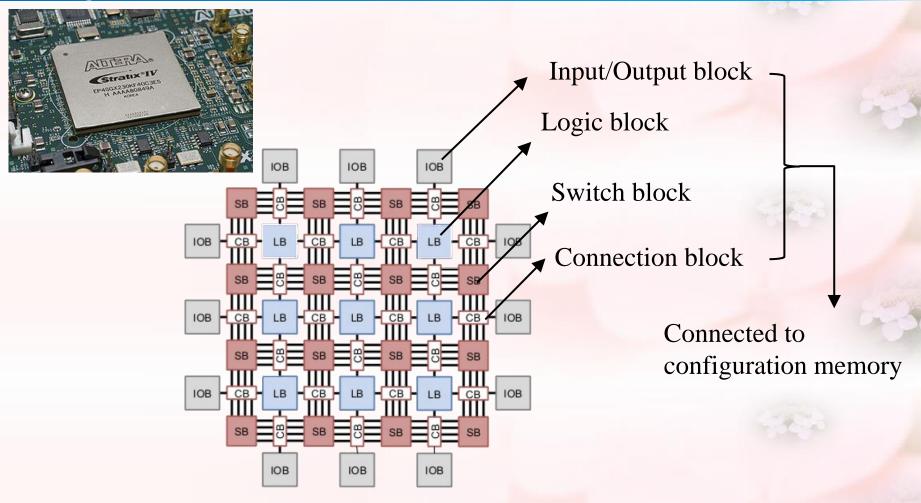

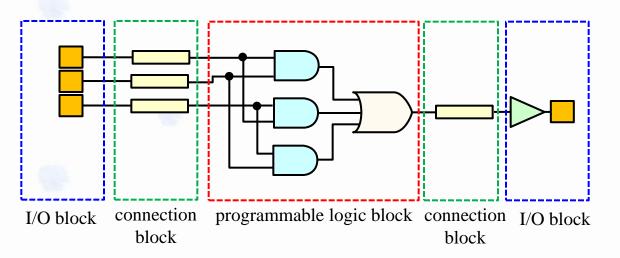

# Configuration of FPGA

# Programming technology

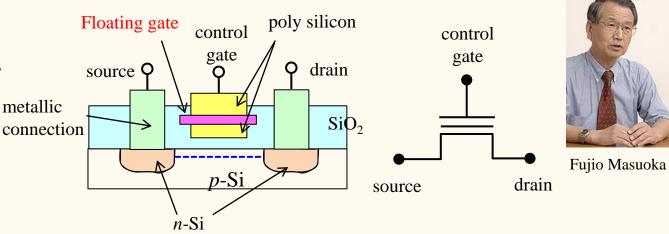

### Flush memory

One of electrically erasable programmable read-only memories (EEPROMs)

Quantum tunneling process charge up/discharge the floating gate

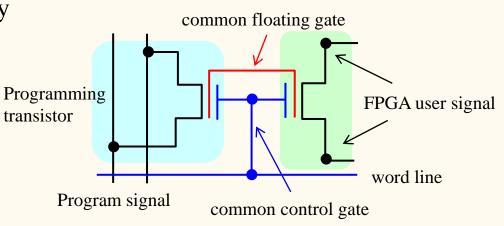

# Programmable switch with flush memory

Programing transistor SD 5 V, control gate -11 V $\rightarrow$  ON, SD0 V, CG16 V  $\rightarrow$  OFF

- Rewritable, non-volatile, small number of device, live at power-up

- Device size is large, on-resistance is high, load capacitance is large, memory lifetime?

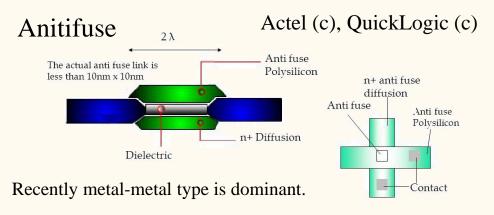

# Programming technology (2)

The inverse process of fusing. That is, short circuit with high voltage and current. Fusing was also used.

- Long, stable memory life. Small device size. Small on resistance.

- Not rewritable. Program needs extra transistors. Available percentage (fidelity) is low.

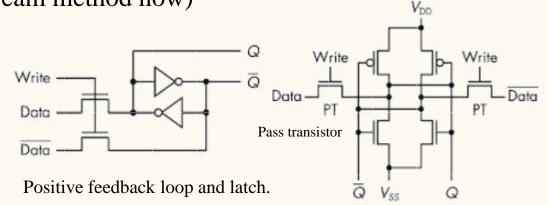

Static memory (SRAM type, mainstream method now)

SRAM does not need refreshing but volatile.

- Large device size, resources, large on resistance, stray capacitance

- State-of-art CMOS technology can be used

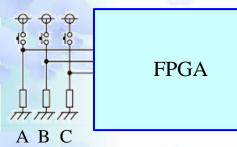

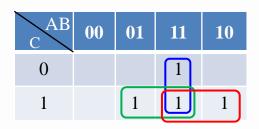

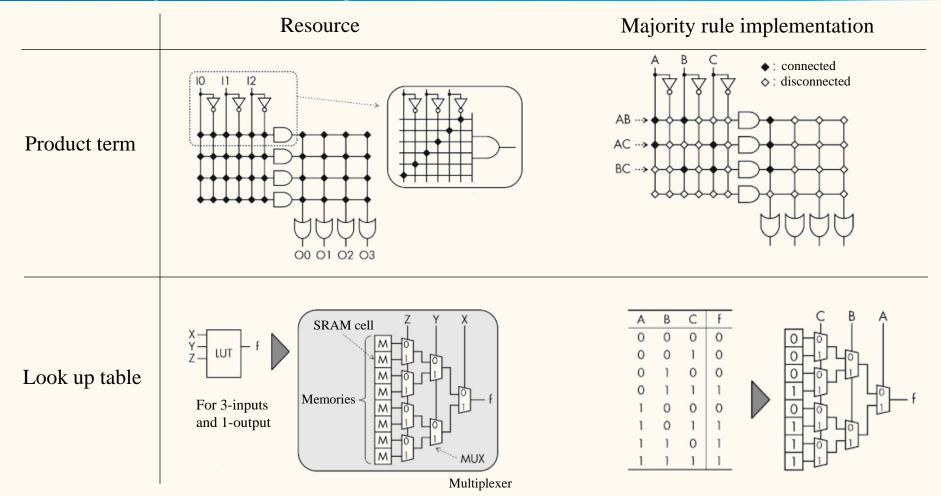

# Simple example of logic block configuration

$\hat{F}$

Μ

Truth table of majority rule

| A | B | С | Μ |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

Circuit level understanding of FPGA

Let us consider a majority rule circuit. The truth table is given.

Karnaugh mapping M=AB+AC+BC (is not required for LUT)

# Various ways to realize logic block

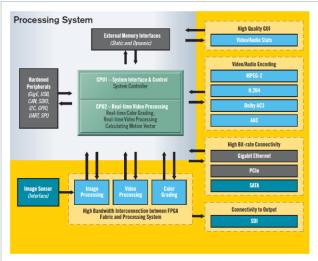

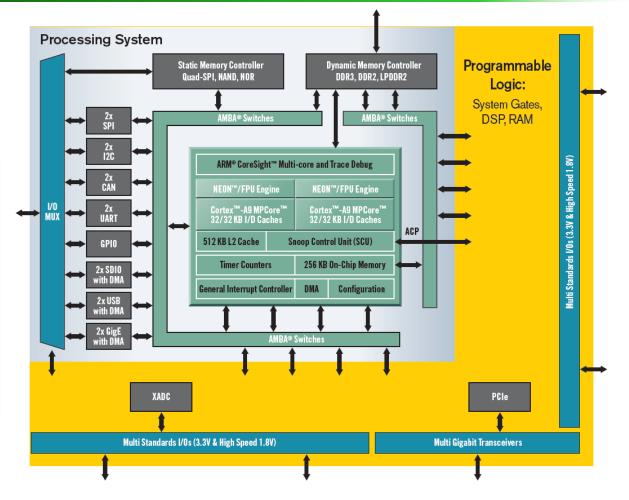

# Advance type FPGA

Integration of DSP, FPU, etc.

(from Xilinx Zynq product brief)

#### BROADCAST CAMERA APPLICATION EXAMPLE

# Hardware description language (HDL)

HDL  $\left\{ \begin{array}{l} VHDL \\ Verilog HDL \end{array} \right\}$

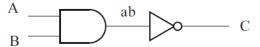

-- Library declaration -----library IEEE; А use IEEE, STD\_LOGIC\_1164.ALL; -- Entity declaration ------В entity NAND\_CIRCUIT is port( A : in std\_logic; B : in std\_logic; C : out std\_logc ); end NAND\_CIRCUIT; -- Architecture declaration -----architecture RTL of NAND\_CIRCUIT is signal ab : std\_logic; begin  $ab \leq A$  and B; C <= not ab; end RTL; RTL: register transfer level

#### VHDL example for

### Translation or High level synthesis (高位合成) or Behavioral synthesis:

| System<br>name | Cyber Work<br>Bench          | Vivado-<br>HLS | Catapult C           | Impulse C                           | Synphony C Compiler | C-to-Silicon<br>Compiler |

|----------------|------------------------------|----------------|----------------------|-------------------------------------|---------------------|--------------------------|

| Company        | <u>NEC</u>                   | <u>Xilinx</u>  | Mentor<br>Graphics   | Impulse Accelerated<br>Technologies | Synopsis            | Cadence                  |

| Language       | System-<br>C/ <u>ANSI</u> -C | <u>C/C++</u>   | ANSIC++/Syste<br>m C | <u>ANSI</u> C                       | <u>C/C++</u>        | System C                 |

Behavior description with high-level languages  $\rightarrow$  Synthesis of HDL codes

Not almighty. Because high-level languages generally use large memories but there are not such size of memories being close to hand in the case of FPGA.

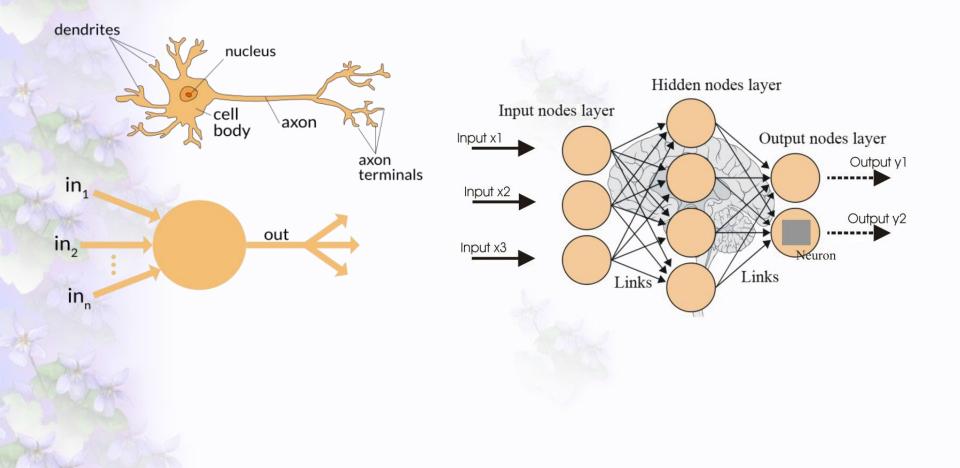

# Neural Network (NN)

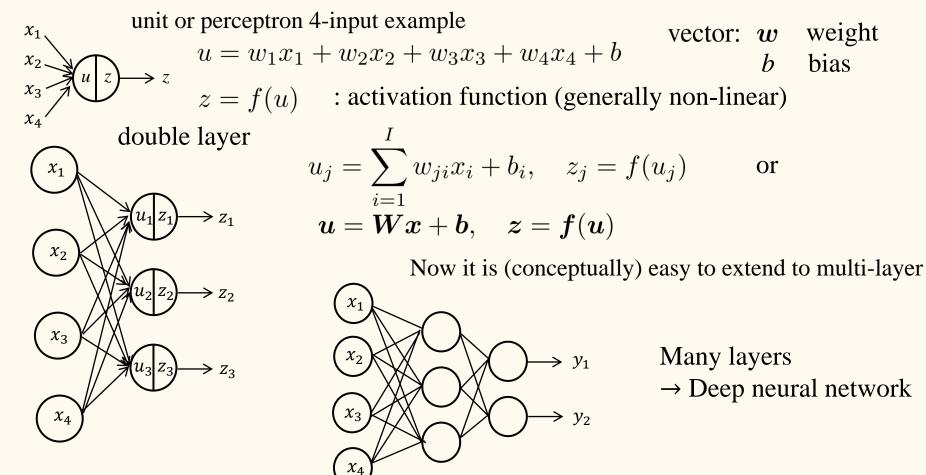

### Feedforward neural network or multi-layer perceptron

# input $x \rightarrow$ desired output d training data $\{(x_1, d_1), (x_2, d_2), \dots, (x_N, d_N)\}$ training samples

Learning: tune w to minimize distance between  $\{d_j\}$  and the network output  $\{y(x_j, w)\}$

$$E(\boldsymbol{w}) = \frac{1}{2} \sum_{n=1}^{N} ||\boldsymbol{d}_n - \boldsymbol{y}(\boldsymbol{x}_n, \boldsymbol{w})||^2 \quad \text{: typical error function} \rightarrow \text{minimize}$$

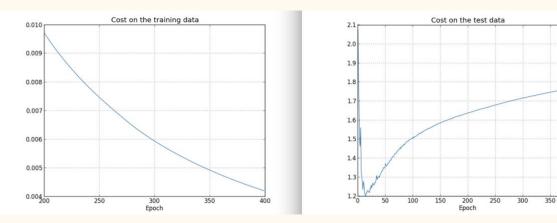

### Overfitting (overlearning) problem:

Trapping to local minima

400

- $\succ$  Back propagation  $\rightarrow$  However this leads to the vanishing gradient problem

- PretrainingDeep belief network (DBN)

- $\rightarrow$  decompose into restricted Boltzmann machine (RBM)

- $\rightarrow$  learning for each RBM

- $\rightarrow$  Transfer to feedforward NN

Autoencorder

### Exceptionally "learnable" NN without pretraining

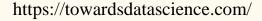

Input:  $W \times W$  image elements:  $x_{ii}$ Filter:  $H \times H$  image elements:  $h_{ii}$ H - 1 H - 1 $u_{ij} = \sum_{p=0} \sum_{q=0} x_{i+p,j+q} h_{pq}$ Pooling > Average > Max

Lp (some point between above)

#### ゼロから作る

Pythonで学ぶディープラーニングの理論と実装

Deep learning from scratch

- Explains from introduction of Python to your PC

- Concise and to the points

- Python examples

# Perceptron expression for logic gates

Perceptron

| eptron | $(x_1)$ | $\Rightarrow y \qquad y = \begin{cases} 0 & (w_1 x_1 + w_2 x_2 \le \theta), \\ 1 & (w_1 x_1 + w_2 x_2 > \theta). \end{cases}$ |

|--------|---------|-------------------------------------------------------------------------------------------------------------------------------|

| AND    |         | $(w_1, w_2, \theta) = (0.5, 0.5, 0.7)$ : just an example                                                                      |

| NAND   |         | $(w_1, w_2, \theta) = (-0.5, -0.5, -0.7)$                                                                                     |

| OR     |         | $(w_1, w_2, \theta) = (0.6, 0.6, 0.5)$                                                                                        |

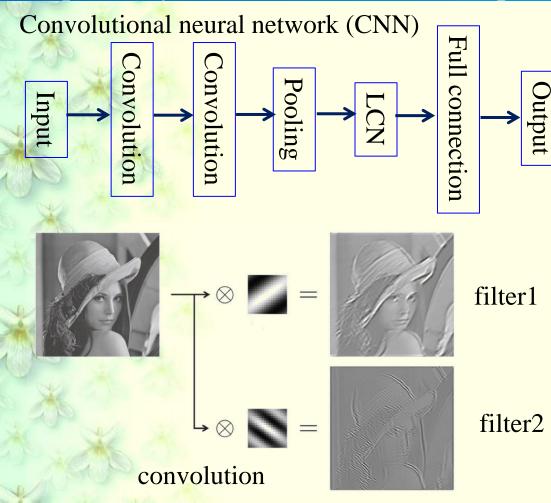

Layer by layer learning calculation  $\rightarrow$  can be done in parallel naturally. Calculation along transition lines  $\rightarrow$  also can be done in parallel.

FPGA card specialized for DNNs (Xilinx)

### Overview

# Supplement for amplifier and noise

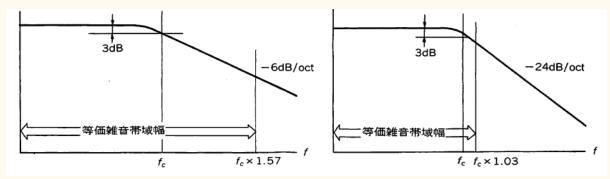

Equivalent noise band width (ENBW)

| Attenuation gradient | k    |

|----------------------|------|

| -6 db/oct            | 1.57 |

| -12 db/oct           | 1.11 |

| -18 db/oct           | 1.05 |

| -24 db/oct           | 1.03 |

gain band width GBW = $A \times f_c$

OP amp. spec. sheet: (open loop gain) × (cut off freq.)

### Supplement amplifier and noise

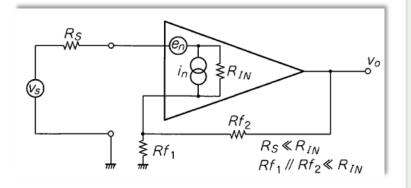

1.  $R_S$  thermal noise =  $\sqrt{4kTR_S}$ 2.  $Rf_1 \parallel Rf_2$  thermal noise =  $\sqrt{4kT(Rf_1 \parallel Rf_2)}$ 3. Input voltage noise  $e_n$ , current noise  $i_n$ 4. Current noise times source resistance =  $i_n \times R_S$ 5. Current noise times feedback resistance =  $i_n \times (Rf_1 \parallel Rf_2)$

(output noise) =

$$\sqrt{e_1^2 + e_2^2 + e_3^2 + e_4^2 + e_5^2} \times G \times \sqrt{\text{ENBW}}$$