# **Chapter 6 Homo-hetero junctions**

So far we have seen the bulk properties of uniform semiconductors. Henceforth we go into the rich physical phenomenon in spatially structures semiconductors, the actions as defices.

### 6.1 Electrical and optical characteristics of homo pn junctions

The pn junction is one of the first semiconductor devices for electric circuits. For the detailed history of the device, see *e.g.* [1] (though in Japanese, out-of-print).

#### 6.1.1 Thermal equilibrium

A pn junction, as it expresses, is a junction of a p-type semiconductor and an n-type semiconductor. Here we consider homojunctions, in which the same species of semiconductor is used for p- and n-layers. In such a junction, the electron density is high in the n-layer and the hole density in the p-layer. Hence there should be diffusion pressures which drive electrons to the p-layer and holes to the n-layer for increase of entropy S. On the other hand, such diffusions charge up the p-layer to negative and the n-layer to positive creating charge double layer at the junction (charge **depletion layer**). This electro-magnetically enhances the internal energy U. In thermal equilibrium, the double layer width is determined from the condition for free energy (U - TS) minimum.

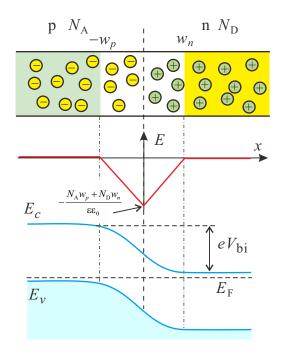

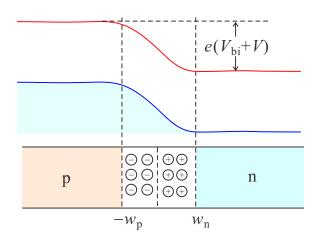

We take a simple model of an abrupt junction (Fig. 6.1), and  $p \sim n \sim n_i$  in the depletion layer. We write the **built-in volt-age** due to the pn structure at the interface across the depletion layer  $V_{\rm bi}$ . In the process that an electron moves from the *n*-layer to the *p*-layer, the energy increases by  $eV_{\rm bi}$ . In the *n*-layer the electron density  $n_n \sim N_{\rm D}$ , and in the *p*-layer the semiconductor equation tells  $n_p \sim n_i^2/N_{\rm A}$ . We consider a general case that  $N_1$  and  $N_2$  electrons are respectively distributed in two boxes with site number N. The number of cases is  $W = {}_N C_{N_1 N} C_{N_2}$ . Here only particle

Fig. 6.1 (a) Schematic of an abrupt pn-junction. (b) Electric field E(x) in depletion layer. x-direction is taken as positive for the field. (c) Band diagram.

exchanges are considered hence  $dN_1 = -dN_2$ . Under assumption  $N \gg N_{1,2}$ ,  $d(\ln W) \approx \ln(N_2/N_1)dN_1$  (mixing entropy of gases). Applying this to the *pn*-junction with  $dN_1 = -1$ ,  $N_1 = n_n$ ,  $N_2 = n_p$ , condition  $d(U - TS)/dn_n = 0$

**Fig.** 6.2 (a) Upper panel: quasi-Fermi levels in a pn-junction under external forward voltage V. Lower panel: Spatial variation of carrier densities. (b) Broken line: I-V characteristics of Shockley theory (eq.(6.11)). Normalized with  $J_0$ , which is the coefficient in eq.(6.11). Solid line: Realistic I-V characteristics, in which series resistance, recombination inside the depletion layer, tunneling through localized states are taken into account. The inset is a linear plot of (6.11).

gives

$$eV_{\rm bi} = k_{\rm B}T \ln \frac{n_n}{n_p} \sim k_{\rm B}T \ln \frac{N_{\rm D}N_{\rm A}}{n_i^2} = E_{\rm g} - k_{\rm B}T \ln \frac{N_c N_v}{N_{\rm D}N_{\rm A}}.$$

(6.1)

$(n_n \sim N_{\rm D}, p_p \sim N_{\rm A}).$

In equilibrium it is also required that the chemical potential (Fermi energy) is constant through the junction, independent of the spatial coordinate. Far inside p, n-layers apart from the junction, the band structure should recover the bulk states. Hence the band diagram in Fig. 6.1(c) is drawn. Let the depletion layer widths in p and n-layers  $w_p$ ,  $w_n$ respectively, then E(x) is given as

$$-\epsilon\epsilon_0 E(x) = N_{\rm A}(2x+w_p) + N_{\rm D}w_n \ (x<0), \quad N_{\rm A}w_p + N_{\rm D}(w_n-2x) \ (x\ge0), \tag{6.2}$$

where  $\epsilon$  is the dielectric constant. Then  $V_{\rm bi}$  is calculated as

$$V_{\rm bi} = \int_{-w_p}^{w_n} (-E(x))dx = \frac{e}{\epsilon\epsilon_0} (N_{\rm D} + N_{\rm A})w_n w_p = \frac{e}{\epsilon\epsilon_0} (N_{\rm D} + N_{\rm A})\frac{N_{\rm D}}{N_{\rm A}}w_n^2 \quad \because w_n N_{\rm D} = w_p N_{\rm A}.$$

(6.3)

From eqs.(6.1) and (6.3), we obtain the relation between the doping concentrations and the depletion layer width.

### 6.1.2 Current-Voltage characteristics

In equilibrium of a pn-junction, the net current is zero as a result of balance between the entropy and the internal energy. An externally applied voltage pushes off the balance and a current flows as a result. When the energy cost is lowered by the voltage, the diffusion current causes **injection of minority carriers**. Minority carrier injection is an action that increases density of minority carrier dynamically. The minority carrier injection breaks the semiconductor equation  $np = n_i^2$  locally. Even in such circumstances, by introducing **quasi-Fermi level**, we can treat electrons and holes as in quasi-equilibriums and apply the Boltzmann equation to obtain carrier fluxes. The semiconductor equation (law of mass action) can also be recovered in a bit modified manner. The goal here is to give the net current as a function of external voltage.

We model the effect of external voltage V as follows. All the voltage drops outside the depletion layer are ignored and V is applied inside it. Far from the junction, the current is carried by majority carriers, which have high concentration and the gradient in the chemical potential in such regions is ignorable. Around the depletion layer, imbalance between the internal energy cost and the increase of entropy causes a flow of carriers. V is applied against  $V_{bi}$  lowering the barrier for diffusion currents, then the majority carriers flows into the counter layers increasing the minority carrier densities at the depletion layer edges. The injected minority carriers diffuse into the bulk, recombine with majority carriers and disappear. The diffusion-annihilation process forms a exponential decay in the steady minority carrier density distribution.

In the above model, we assume that local thermal equilibrium is attained in each thin layer parallel to yz plane through the carrier-carrier interaction and the particles can be exchanged between neighboring layers. Quasi-Fermi levels, which depends on x-coordinate, for electrons ( $\mu_e(x)$ ) and holes ( $\mu_h(x)$ ) are introduced as follows,

$$n(x) = N_c \exp[-(E_c(x) - \mu_e(x))/k_{\rm B}T], \quad p(x) = N_v \exp[-(\mu_h(x) - E_v(x))/k_{\rm B}T], \tag{6.4a}$$

*i.e.*,

$$\mu_e(x) = E_c(x) + k_{\rm B}T \ln \frac{n(x)}{N_c}, \quad \mu_h(x) = E_v(x) - k_{\rm B}T \ln \frac{p(x)}{N_v}.$$

(6.4b)

The diffusion of minority carriers (densities  $n_p$ ,  $p_n$ ) is described by the following diffusion equations.

$$D_e \frac{d^2 n_p}{dx^2} = \frac{n_p - n_{p0}}{\tau_e} - G(x), \quad D_h \frac{d^2 p_n}{dx^2} = \frac{p_n - p_{n0}}{\tau_h} - G(x), \tag{6.5}$$

where G(x) represents minority carrier creation *e.g.* by light illumination and in the dark G(x) = 0.  $n_{p0}$ ,  $p_{n0}$  are minority carrier concentrations in the bulk regions,  $D_{e,h}$ ,  $\tau_{e,h}$  are the diffusion constant and the lifetime respectively (*e* for electrons, *h* for holes). Then **minority carrier diffusion lengths** for electrons and holes are

$$L_e = \sqrt{D_e \tau_e}, \quad L_h = \sqrt{D_h \tau_h}.$$

(6.6)

The solution for (6.5)  $(p_n \text{ for } x > w_n, n_p \text{ for } x < -w_p)$  which satisfies the boundary condition  $n_p \to n_{p0} (x \to -\infty)$ and  $p_n \to p_{n0} (x \to \infty)$ , is obtained as

$$n_p(x) = \delta n_0 \exp\left(\frac{x+w_p}{L_e}\right) + n_{p0}, \quad p_n(x) = \delta p_0 \exp\left(-\frac{x-w_n}{L_h}\right) + p_{n0},$$

(6.7)

where  $\delta n_0$ ,  $\delta p_0$  are concentrations of injected minority carriers at the edges of the depletion layer. From the definition (6.4b), in the region of diffusion and with ignoring  $n_{p0}$ ,  $p_{n0}$  in (6.7), the quasi-Fermi levels linearly depend on the distances as

$$\mu_e(x) = E_c + k_{\rm B}T \left[ \frac{x + w_p}{L_e} + \ln \frac{\delta n_0}{N_c} \right], \quad \mu_h(x) = E_v - k_{\rm B}T \left[ \frac{x - w_n}{L_h} + \ln \frac{\delta p_0}{N_v} \right].$$

(6.8)

These should join the bulk values  $E_{\rm F}^{(p),(n)}$  at  $x \to \pm \infty$  respectively and  $E_{\rm F}^{(p),(n)}$  differ by eV, *i.e.*,  $E_{\rm F}^{(p)} - E_{\rm F}^{(n)} = eV$ . Therefore they are schematically drawn as in Fig. 6.2(a).

We ignore electron-hale recombination inside the depletion layer and assume the currents are limited by the diffusion of minority carriers. Then the net current density is the sum of minority carrier diffusion currents at the two edges of the depletion layer. From eq.(6.7) and eq.Fig. 6.2(a),

$$\delta n_0 + n_{p0} = n(-w_p) = n_{p0} \exp \frac{eV}{k_{\rm B}T}, \quad \delta p_0 + p_{n0} = p(w_n) = p_{n0} \exp \frac{eV}{k_{\rm B}T}.$$

(6.9)

The electron diffusion current density at  $x = -w_p$  in the process (6.5) is thus

$$j_{e} = eD_{e} \left. \frac{dn_{p}}{dx} \right|_{-w_{p}} = \frac{eD_{e}\delta n_{0}}{L_{e}} = \frac{eD_{e}}{L_{e}}n_{p0} \left[ \exp \frac{eV}{k_{\rm B}T} - 1 \right].$$

(6.10)

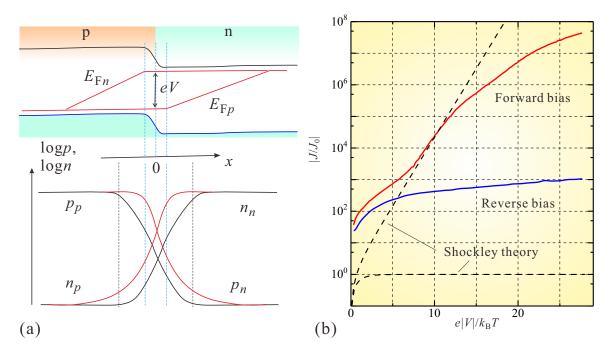

Fig. 6.3 (a) Carrier density distribution around a *pn*-junction under photo-generation of minority carriers G. Depletion layer edges are indicated by perpendicular broken lines. Bias is taken as shortage V = 0. (b) Schematic I-V characteristics in the dark and under illumination.

The hole current can be calculated in the same way and the net current is given as

$$j = e \left[ \frac{D_e}{L_e} n_{p0} + \frac{D_h}{L_h} p_{n0} \right] \left[ \exp \frac{eV}{k_{\rm B}T} - 1 \right] \approx e n_i^2 \left[ \frac{D_e}{L_e N_{\rm A}} + \frac{D_h}{L_h N_{\rm D}} \right] \left[ \exp \frac{eV}{k_{\rm B}T} - 1 \right].$$

(6.11)

Equation (6.11) is the very basics of the Schottky theory of pn-junction. Though the model grabs the essence, real pn junctions are much more complicated. Important modifications are series resistance, recombination in depletion layer and tunneling conductance through localized level inside energy gap (parallel Ohmic resistance). With these modifications, a realistic characteristics shown in Fig. 6.2(b) differs considerably from the Shockley theory.

#### 6.1.3 Photo-response of *pn*-junctions

Let us take the simplest model for a *pn*-junction under illumination assuming majority carrier generation G(x) does not depend on x (a constant G) in the diffusion equation (6.5). Just as before, the solution for  $n_p(x)$  and  $p_n(x)$  which satisfies the boundary condition  $n_p \to n_{n0} + G\tau_e$  for  $x \to -\infty$ , and  $p_n \to p_{n0} + G\tau_h$  for  $x \to \infty$  is

$$n_p(x) = n_{p0} + G\tau_e + \left[ n_{p0} \left( \exp\left(\frac{eV}{k_{\rm B}T}\right) - 1 \right) - G\tau_e \right] \exp\left(\frac{x + w_p}{L_e}\right), \tag{6.12a}$$

$$p_n(x) = p_{n0} + G\tau_h + \left[p_{n0}\left(\exp\left(\frac{eV}{k_{\rm B}T}\right) - 1\right) - G\tau_h\right]\exp\left(-\frac{x - w_n}{L_h}\right).$$

(6.12b)

The solution for V = 0 is schematically drawn in Fig. 6.3(a).

From the solution, the net current density is given as

$$j = j_0 \left[ \exp \frac{eV}{k_{\rm B}T} - 1 \right] - eG(L_e + L_h), \tag{6.13}$$

where  $j_0$  is the coefficient in front of the parentheses in (6.11). Equation (6.13) is a simple negative shift of (6.11) by  $j_{sc} \equiv G(\tau_e + \tau_h)$ . Figure 6.3(b) shows the characteristics. Real solar cells are more complicated but the common is the negative shift of the current characteristics with illumination. The parameters which characterize each device are the negative shift at short-circuit condition  $|J_{SC}|$  (short circuit current) and the voltage at open-circuit condition  $V_{OC}$  (open circuit voltage). These depend, of course, on the strength and the spectrum of illumination.

In the characteristics shown in Fig. 6.3(b), the cell pumps out an electric energy under the bias condition in the fourth quadrant. Current J and voltage V give power W = |JV|. In the forth quadrant  $|J| \le |J_{SC}|$ ,  $|V| \le |V_{OC}|$  then  $W \le |J_{SC}V_{OC}|$ . Then  $J_{max}$ ,  $V_{max}$  which give the maximum power is determined and

$$FF \equiv \frac{J_{\max}V_{\max}}{J_{SC}V_{OC}} \le 1$$

(6.14)

is called **filling factor** (FF). The better the squareness of the I-V characteristics, the higher the FF.  $J_{SC}$ ,  $V_{OC}$ , and FF are useful parameters for discussing phenomenology of solar cells, modeling equivalent circuits. In the ideal characteristics (6.13),

$$J_{\rm SC}| = eG(L_e + L_h), \quad V_{\rm OC} = \frac{k_{\rm B}T}{e} \ln\left[\frac{eG(\tau_e + \tau_h)}{j_0} + 1\right].$$

(6.15)

The above is the basics of photoelectric conversion and applied to *e.g.* solar cells. For the solar cells see the article by the present author [2] (in Japanese).

## 6.2 *pn*-junction transistors

From left, John Bardeen, William Shockley, Walter Brattain. At AT&T Bell Laboratories, in 1948.

Today, we see two kinds of semiconductor devices invented by a genius named William Shockley. The style of research and development which he began, as well as his devices, has been changing the human life. The above expression is not exaggeration, I believe. I have read a short commentary, which tells "the researchers in Bell Labs. were doing basic research on the surface states of Ge with putting tips on the surfaces and accidentally found the transistor action". But this is far from real situation. Walter Brattain and John Bardeen, who were the direct finders, were doing research aiming at construction of "solid state amplifier" under the team leader Shockley. They did not expect such an easy finding probably but they realized the amplification certainly because they were doing such objective research.

The experiment was done a little before the Christmas of 1947 (said to be 12/16. The application for patent was 12/23) Shockley was out of the labs for a journey. He was thus not so glad hearing the success. Also the transistor (the term is a combination of transfer

and resistor) which Brattain and Bardeen accidentally found was called "point contact type", unstable, had low reproducibility. It should have serious obstacles for commercial viability. Their finding might have stimulated Shockley's fight as an inventor, he was absorbed in thought as a theorist aiming at realization of "reproducible device for amplification" and finally got the brilliant inspiration of junction transistor, on the new year's eve allegedly. The theory for the junction transistor established 1/23 in the next year. The experimental realization was a year later. The event was the glorious dawn of the semiconductor physics, in which artificial structures in solids utilize the structural sensitivity of semiconductors and create new functions, new stages of physics[3].

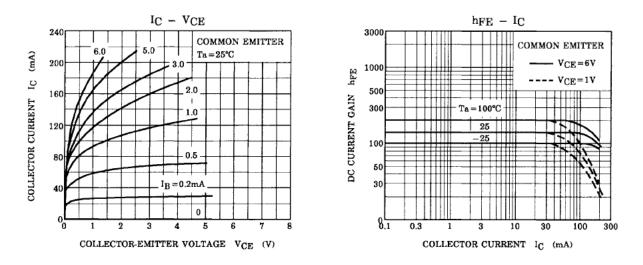

### 6.2.1 Junction transistor: structure

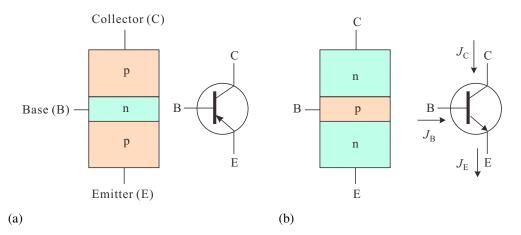

Figure 6.4 shows basic structure of **junction transistor** (Bipolar Junction Transistor, BJT, at times just "bipolar transistor"), in which two *pn*-junctions are placed close to each other. *npn* and *pnp* are possible types of junctions. An ohmic contact to the central layer is required for the device to have three terminals. The terminals at the two ends are called **Collector** (C), **Emitter** (E) respectively and the central one is called **Base** (B). In the very beginning, the structure was fabricated with alloying metals which work as dopants to both sides of the base material. The naming "Base" came from the fact though lithography and thermal diffusion, ion implantation and epitaxy soon became the dominant methods. As we will see for the transistor action, the base should be very thin. Thinner than the minority carrier diffusion length.

**Fig.** 6.4 (a) Schematic structure of pnp transistor. Circuit symbol and the names of terminals. (b) Schematic structure of npn transistor and the circuit symbol.

Circuit symbols of transistors are shown in Fig. 6.4, which represent connections of two electrodes to the base graphically. Circles are often omitted. *pnp* and *npn* are distinguished with the direction of arrow, which indicates direction of electric current when minority carriers are injected into the base electrode. Below we consider *npn*-type and define the directions of the current as in the figure.

### 6.2.2 Current-amplification of junction transistors

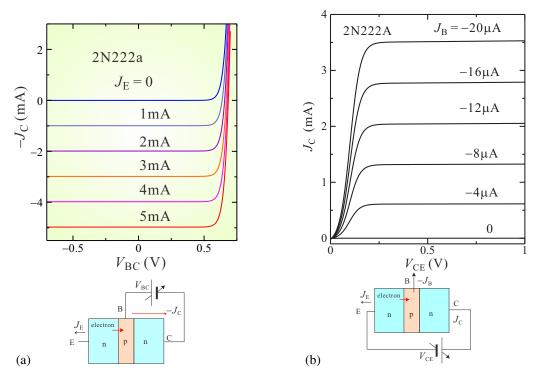

In the first experiment a constant voltage source is connected to B-C and collector current  $J_{\rm C}$  is measured. Inside the structure B-C is nothing but a *pn* diode and the result is a well known rectification characteristics ( $J_{\rm E} = 0$  in Fig. 6.5(a)). Now we connect a constant current source between E and B, and apply finite currents through E. Because B-E is also a *pn* junction, the forward bias is positive for B. As shown in Fig. 6.5(a)  $V_{\rm BC} - J_{\rm C}$  curve shifts parallely to negative. The amount of shift is almost  $J_{\rm E}$ .

It should be noted that the characteristics is close to that of a solar cell shown in Fig.2.3(b). The similarity is not a coincidence, rather, the physical situation is almost the same. While In a solar cell, the minority carriers are directly created by photon irradiation, in a transistor, the minority carriers are injected through the pn junction between E and B to the other junction between B and C.

The phenomenon occurring in the junctions are summarised as follows. Here we only describe the phenomenon in conduction band while that in valence band can be discussed in parallel. In an npn junction, a reverse bias voltage to B(p)-C(n) suppresses the diffusion current from the *n*-layer to the *p*-layer. The (reverse) diffusion of *electrons* from the *p*-layer to the *n*-layer is not enhanced by the reverse bias because all the electrons reach from the *p*-layer to the junction are swung to the *n*-layer and it is already saturated at zero-bias. Under the reverse (or zero) bias condition of  $V_{\rm BC}$ , let the other *pn*-junction (E-B) be under a forward bias condition. This is possible because an Ohmic contact is attached to the base electrode, hence  $V_{\rm EB}$  and  $V_{\rm BC}$  can be controlled independently. The forward bias lowers the barrier by the built-in potential in E-B junction and the electrons (majority in the *n*-layer) diffuse into the base layer and the minority carrier **concentration** increases in B. This is the phenomenon called **minority carrier injection**, which decays over the **minority carrier diffusion length** through the recombination with majority carriers (holes). Note that the continuity in current is hold. The flow by injected electrons is not driven by the electrode (the recombination current goes to the electrode). When the B-layer is much thinner than the minority carrier diffusion length, most of the injected carriers reach the other junction enhancing the *reverse current*. In Fig. 6.6(a), this appears as the enhancement of the reverse current, the amount of which is determined that of injected minority carriers. Hence the current does not depend on  $V_{\rm BC}$  as long

**Fig.** 6.5 (a)  $J_{\rm C}$  (upside down for convenience) as a function of  $V_{\rm BC}$  with  $J_{\rm E}$  as a parameter in the circuit shown in the lower panel. With increasing  $J_{\rm E}$  *i.e.*, injecting electrons from E to B, the characteristics resembles to that of an illuminated solar cell. (b) Application of collector-emitter voltage  $V_{\rm CE}$  with floating B, almost no current flows due to the reverse bias in C-B. The biasing B with some currents  $J_{\rm C}$  appears according to  $J_{\rm B}$  showing saturation for  $V_{\rm CE}$ .

as there is no forward current.

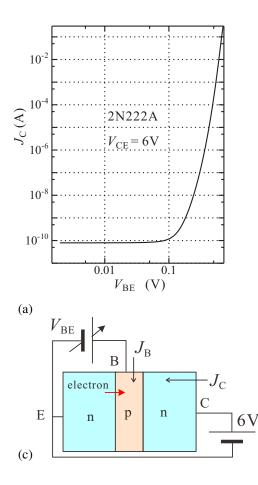

Now an amplification circuit can be composed as follows. Let the electrodes C-E be voltage biased as in Fig. 6.6(c). The amount of minority carrier injection into B-layer is determined by  $V_{BE}$ . Hence in this circuit  $J_C$  strongly depends on  $V_{BE}$  as shown in Fig. 6.6(a). However, the relation is too non-linear for the use of the device in a voltage-input circuit.

Some of the injected minority carriers recombine with majority carriers and some portion flows out to B-electrode. The base current  $J_{\rm B}$  depends on  $V_{\rm BE}$  in the same functional form only but the coefficient as  $J_{\rm C}$  because the *pn*-junction is the same.  $J_{\rm C}$  is thus proportional  $J_{\rm B}$ , that is,

$$J_{\rm C} = h_{\rm FE} J_{\rm B}.\tag{6.16}$$

The good linearity is confirmed in the measurement as shown in Fig. 6.6(b).  $h_{\rm FE}$  is called **current amplification factor**. And it is often said that "a bipolar transistor works as a current amplification device" from this face. This is in practice, true as long as we use it as a black box device in electric circuits. However in physical mechanism, as discussed above, there is no such causality that a small current drives a larger current. The following expression may be closer to reality: a small current here is just a monitor for voltage to control a large current.

In the usage of a BJT in a circuit, care should be taken that (because it is a "current amplification device") the input voltage bias should be set to a low differential resistance region. Particularly in high frequency circuits, the impedance matching should be taken to the characteristic impedance of the transmission line. One simple "rule" for transistor circuits is that when a transistor is working as an amplifier, the base-emitter bias voltage should be around the quasi-threshold voltage (though as we saw there is no threshold voltage in *pn*-junctions, in ordinary circuit scale, the I-V curve seems as if it has).

**Fig.** 6.6 Characteristics of a transistor measured in a experimental circuits shown in (c). (a) C-E is biased with 6 V and the voltage between B-E ( $V_{\rm BE}$ ) is varied.  $J_{\rm C}$  strongly depends on  $V_{\rm BE}$ . (b)  $J_{\rm C}$  is re-plotted as a function of  $J_{\rm B}$  and (because outputs of the same diode is observed) very good linearity is obtained. The inset shows a log-log plot with a broken line indicating slope 1.

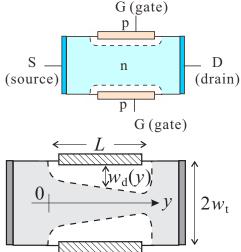

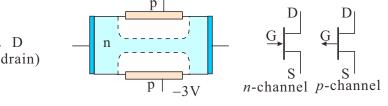

# 6.3 Field effect transistors I

Field Effect Transistors (FETs) are now used much more widely in circuits than BJTs. And the idea of FET was born even long before that of BJT <sup>\*1</sup>, but for the realization of FET requires technologies even higher than those for BJT and the realization was later than that for BJT. In these 20 years, Metal-Oxide-Semiconductor (**MOS**) type FETs are mainly used but the first FET was realized for Junction FET (JFET), which utilize *pn* junctions.

#### 6.3.1 *pn*-junction and depletion layer

For understanding the device action of JFET, the relation between the reverse bias voltage and the depletion layer is important. We consider a *pn*-junction shown in Fig. 6.7, with *x*-dependent potential  $\phi(x)$ . The Poisson equation is given as

$$\frac{d^2\phi}{dx^2} = -aq(x) \quad (a \equiv (\epsilon\epsilon_0)^{-1}). \tag{6.17}$$

In the space-charge region (depletion layer) we assume abrupt concentration distribution of dopants and sharp cutting of the end of depletion layer. Then

$$\begin{cases} q = -eN_A & (-w_p \le x \le 0), \\ q = eN_D & (0 \le x \le w_n). \end{cases}$$

(6.18)

<sup>\*1</sup> Shockley wrote a patent on FET before BJT though many similar ideas had existed before that. We cannot say the patent is as unique as that of BJT.

Fig. 6.7 Simple model of a pn junction

Let's take the asymptotic condition as  $\phi(-\infty) = 0$ . When there is external reverse bias voltage V, the boundary condition at the edges of depletion layer is  $d\phi$

$$\phi(-w_p) = 0, \qquad \left. \frac{d\phi}{dx} \right|_{-w_p} = 0,$$

$$\phi(w_n) = V + V_{\rm bi}, \qquad \left. \frac{d\phi}{dx} \right|_{w_n} = 0.$$

(6.19)

Integration of the above gives

$$\phi(x) = \begin{cases} (aeN_A/2)(x+w_p)^2 & (-w_p \le x \le 0), \\ V+V_{\rm bi} - (aeN_D/2)(x-w_n)^2 & (0 \le x \le w_n). \end{cases}$$

(6.20)

From the condition for the connection at x = 0

$$\lim_{x \to +0} \phi = \lim_{x \to -0} \phi, \quad \lim_{x \to +0} (d\phi/dx) = \lim_{x \to -0} (d\phi/dx),$$

(6.21)

the widths of depletion layer  $w_p$ ,  $w_n$  are given as follows.

$$w_p = \left[\frac{2\epsilon_0\epsilon(V+V_{\rm bi})}{eN_A} \cdot \frac{N_D}{N_D+N_A}\right]^{1/2}, \quad w_n = \left[\frac{2\epsilon_0\epsilon(V+V_{\rm bi})}{eN_D} \cdot \frac{N_A}{N_D+N_A}\right]^{1/2} \tag{6.22}$$

$$w_d = w_p + w_n = \left[\frac{2\epsilon_0\epsilon(V+V_{\rm bi})}{e} \cdot \frac{N_A + N_D}{N_A N_D}\right]^{1/2}.$$

(6.23)

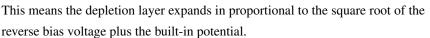

The charge accumulated in the depletion layer on *n*-side is  $Q = eN_Dw_d$  per unit area giving the effective capacitance (differential capacitance) as

$$\frac{dQ}{dV} = eN_D \sqrt{\frac{2\epsilon\epsilon_0}{eN_D}} \frac{1}{2\sqrt{V+V_{\rm bi}}} = \sqrt{\frac{\epsilon\epsilon_0 eN_D}{2}} (V+V_{\rm bi})^{-1/2}.$$

(6.24)

In a  $p^+n$ -structure, that is,  $N_A \gg N_D$ ,

$$w_d \approx \left[\frac{2\epsilon\epsilon_0(V+V_{\rm bi})}{eN_D}\right]^{1/2} \approx w_n.$$

(6.25)

This relationship is frequently used for characterization of pn-junctions. For example, differential capacitance C(V) can be measured with applying high frequency voltage source with a small amplitude and through the phase shift. We plot the data as shown in the left figure (for the convenience, the horizontal axis is taken to -V),  $1/C^2$  versus -V. If  $N_D$  is spatially uniform, the data points should be aligned on a line. (6.24) is

valid only for V > 0 and  $C \to \infty$  cannot be realized. But with extrapolation from V > 0 the point  $1/C^2 = 0$  can be specified and we obtain  $V_{\text{bi}}$  from this.

When  $N_D$  is not uniform spatially or some deep level traps exist, we obtain information of the spatial distribution from differentiating the plot. Application of pulses in V and analysis of transient response under light illumination or related techniques can bring much of the information inside the semiconductor[4].

### 6.3.2 Junction Field Effect Transistors

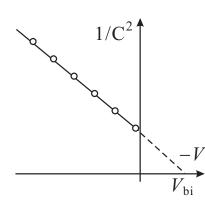

Figure 6.8 shows a schematic drawing of the JFET structure in a cross sectional view. It is for an *n*-channel, which has two electrodes on the both edges. They are called **Source** (S) and **Drain** (D) respectively. The channel is sandwiched by  $p^+$  layers called **Gates** (G).

The principle of device action is very simple as can be seen in Fig. 6.8. Applying reverse bias to the gates causes expansion of white-colored depletion layer according to eq.(6.23). This makes the conduction channel narrower and enhances the channel resistance up to infinity for pinch-off. Thus the current through the device is controlled by the gate voltage. This is apparently a voltage-controlled device and the input impedance is typically resistance of pn-junction in reverse bias condition. So it is classified into high input impedance device.

A characteristic feature here is that a large source-drain current causes a significant voltage drop across the device, resulting in gradient of effective reverse bias voltage for the channel-controlling depletion layer. Let us see a simple model. As before in the model for pn-junctions, we assume the boundaries between depletion layers and conduction channel are abrupt. Let the gate length L, the thickness of JFET  $2w_t$ . We take the channel direction along y-axis. The depletion layer with  $w_d$  is

$$w_d(y) = \sqrt{\frac{2\epsilon\epsilon_0 V(y)}{eN_D}},\tag{6.26}$$

where V(y) is local voltage at position y between the channel and the gate. V(y) can be obtained by subtracting voltage along the channel  $V_{ch}$  due to the source-drain current from the sum of the built-in potential  $V_{bi}$  and the reverse bias gate voltage  $V_{g}$ .

$$V(y) = V_{\rm g} + V_{\rm bi} - V_{\rm ch}(y).$$

We have no injection of minority carrier and only consider the drift current of majority carriers. The electric field along y-direction is dV/dy. Let the channel depth W and the drift current through the channel is

$$J_{ch} = eN_D \mu_n \frac{dV}{dy} \cdot 2(w_t - w_d)W.$$

(6.27)

**Fig.** 6.8 Schematic structure of JFET (*n*-channel) (upper left panel). A cross-sectional view. The easiest way to form the  $p^+$ -layer is alloying the metal, which can work as acceptor inside the semiconductor. The picture in the center shows the way the depletion layer expand (white region) with application of reverse bias to the gates. The upper left shows circuit symbols. The (lower) left shows the dimensions of the model adopted in the text.

In steady state there is no charging up and  $J_{ch}$  is uniform through the channel thus integration over the channel should be  $J_{ch}L$ .

$$J_{\rm ch}L = \int_0^L J_{\rm ch}dy = 2eN_D\mu_n W \int_0^L (w_t - w_d) \frac{dV}{dy} dy = 2w_t eN_D\mu_n W \int_{V_0}^{V_L} \left(1 - \frac{w_d}{w_t}\right) dV.$$

(6.28)

Let the critical voltage  $V_c$  at which the channel is pinched ( $w_d = w_t$ ) and  $J_{ch} = 0$  then  $V_c = eN_D w_t^2/2\epsilon\epsilon_0$ . Hence from  $w_d/w_t = \sqrt{V/V_c}$ ,  $J_{ch}$  in this model is obtained as

$$J_{\rm ch} = \frac{2N_D e\mu_n W w_t}{L} \left[ V_L - V_0 + \frac{2}{3\sqrt{V_c}} (V(V_0)^{3/2} - V(V_L)^{3/2}) \right].$$

(6.29)

In eq.(6.29), at small voltages, the first linear term in  $V_L$  is dominant and  $J_{ch}$  increases linearly. With increasing the voltage, the last  $V_L^{3/2}$  term grows and at last the current begins decreasing, which means negative differential resistance. In actual device, this does not occur and  $J_{ch}$  simply saturates with increasing V. The model contains various shortages, *e.g.*, the equipotential lines are straight and along x-axis. Improved models can reproduce the saturation but they are inevitably complicated. There are also empirical analytical formulas well fit to the experiments but they have no physical reasoning.

# Appendix 6A: Analysis of pn junction transistor

Let us have a brief look at the simplest analysis of charrier statistics in bipolar transistors.

### 6A.1 Current-voltage characteristics

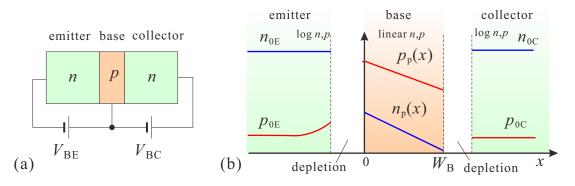

Figure 6A.1 illustrates the bias conditions and the carrier concentrations in an npn-type transistor. We take the x-axis along the device current direction, and the depletion layer edge at the emitter side of the base is set to x = 0. The electron (minority carrier) concentration at x = 0 is

$$n_p(0) = n_{p0} \exp \frac{eV_{\rm BE}}{k_{\rm B}T}.$$

(6A.1)

They diffuse the base region and reach the depletion edge at the other side  $x = W_{\rm B}$ . From there the electrons are immediately swept out to the collector by the electric field in the depletion layer. Hence the electron concentration in the vicinity of  $W_{\rm B}$  should be very small.

$$n_p(W_{\rm B}) = n_{p0} \exp \frac{-eV_{\rm BC}}{k_{\rm B}T} \approx 0.$$

(6A.2)

Providing that  $W_{\rm B}$  is much shorter than the minority carrier diffusion length, we can ignore the carrier recombination and the diffusion current in the base is constant. Equation (5.12) tells the current is proportional to  $dn_p/dx$ . Hence  $n_p$  varies

**Fig.** 6A.1 (a) Biasing condition of the npn transistor under consideration. (b) Schematic diagram of carrier concentrations in a npn type transistor. In the base the ordinate is in linear scale while logarithmic in other regions.

Fig. 6A.2 Characteristics of transistor 2SC1815 for small signal amplification (from the datasheet). Left panel: Collector-emitter voltage  $V_{\rm CE}$  dependence of collector current  $J_{\rm C}$  for various base current  $J_{\rm B}$ .

linearly against x as illustrated in the figure (the concentration is in the linear scale only in the base region). Hence from (6A.2) the diffusion current density in the base is

$$j_{\mathrm{D}e} = -D_e \frac{dn_p}{dx} \approx e D_e \frac{n_p(0)}{W_{\mathrm{B}}}.$$

(6A.3)

This is the major part of the collector current and the collector current is with A as the cross setion of the device,

$$J_{\rm C} = eAD_e \frac{n_p(0)}{W_{\rm B}}.$$

(6A.4)

From the semiconductor equation  $n_{p0} \approx n_i^2 / N_A$ ,

$$J_{\rm C} \approx \frac{eAD_e n_{p0}}{W_{\rm B}} \exp \frac{eV_{\rm BE}}{k_{\rm B}T} \approx \frac{eAD_e n_i^2}{W_{\rm B}N_{\rm A}} \exp \frac{eV_{\rm BE}}{k_{\rm B}T} \equiv J_{\rm S} \exp \frac{eV_{\rm BE}}{k_{\rm B}T}.$$

(6A.5)

$J_{\rm S} = eAD_e n_i^2 / W_{\rm B} N_{\rm A}$  is the coefficient which is inversely proportional to  $W_{\rm B} N_{\rm A}$ .

On the other hand, the base  $\rightarrow$  emitter is in forward biasing condiction while base  $\rightarrow$  collector is reverse biased. Hence most of the base current flows to the emitter, which is determined by the hole diffution current in the emitter. The calcution is along the same line as the above collector current and the diffusion part of the base current is

$$J_{\rm Bh} = \frac{eAD_h}{L_h} p_{n\rm E}(0) = \frac{eAD_h}{L_h} p_{n\rm E0} \exp \frac{eV_{\rm BE}}{k_{\rm B}T} = \frac{eAD_h}{L_h} \frac{n_i^2}{N_{\rm D}} \exp \frac{eV_{\rm BE}}{k_{\rm B}T}.$$

(6A.6)

In the base, minority carrier concentration is enhanced and the recombination current may give some contribution. The total charge of the minority carriers is  $Q_e = -en_p(0)W_BA/2$ . Let  $\tau_b$  be the minority carrier life time and the recombination current is

$$J_{\rm Br} = \frac{Q_e}{\tau_b} = \frac{e n_p(0) A W_{\rm B}}{2\tau_b} \exp \frac{e V_{\rm BE}}{k_{\rm B} T}.$$

(6A.7)

Therefore the base current is written as the sum of the above as

$$J_{\rm B} = eA\left(\frac{D_h}{L_h}\frac{n_i^2}{N_{\rm D}} + \frac{n_{p0}W_{\rm B}}{2\tau_b}\right)\exp\frac{eV_{\rm BE}}{k_{\rm B}T}.$$

(6A.8)

Then from (6A.5) and (6A.8), the current gain is obtained as

$$h_{\rm FE} = \left(\frac{D_h}{D_e} \frac{W_{\rm B}}{L_h} \frac{N_{\rm A}}{N_{\rm D}} + \frac{W_{\rm B}^2}{2\tau_b D_e}\right)^{-1}.$$

(6A.9)

### 6A.2 Effect of depletion layer width

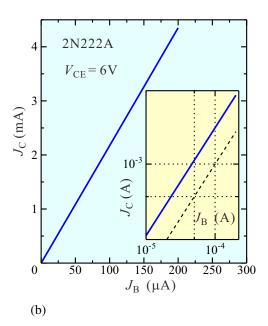

Figure 6A.2 shows the characteristics of a transistor numbered 2SC1815 (Toshiba, Co. Ltd.). The right panel shows  $h_{\rm FE}$  as a function of  $J_{\rm C}$ .  $h_{\rm FE}$  is almost constant in the low  $J_{\rm C}$  region indicating good linearity. On the other hand, the left panel shows  $J_{\rm C}$  as a function of  $V_{\rm CE}$  with  $J_{\rm B}$  as a parameter. In this panel, in the region  $V_{\rm CE} \approx 0$ , the base-collector is forward biased and not in the region of current amplification. Even in the current amplificatio region,  $J_{\rm C}$  increases with  $V_{\rm CE}$ . This is called the Early effect caused by the widening of the depletion layer thus by the thinning of the base width  $W_{\rm B}$ .

Let  $\Delta W$  be the variation in the width of base width and the collector current is given as

$$J_{\rm C} = eAD_e \frac{n_p(0)}{W_{\rm B} - \Delta W} \approx eAD_e \frac{n_p(0)}{W_{\rm B}} \left(1 + \frac{\Delta W}{W}\right) \equiv J_{\rm C0} \left(1 + \frac{\Delta W}{W}\right).$$

(6A.10)

$\Delta W$  grows rapidly with  $V_{\rm CE}$  as in (6.23) when  $V_{\rm CE}$  is small while the rate lowers with  $V_{\rm CE}$ . In Fig. 6A.2, such tendency is apparent. In Fig. 6.5(b), the Early effect is small and the increase in  $J_{\rm C}$  can be approximated to be linear in  $V_{\rm CE}$ .

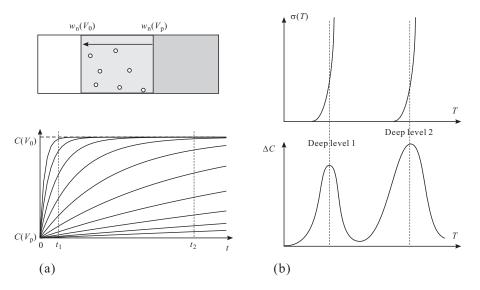

### 付録 6B: Deep level transient spectroscopy (DLTS)

Here I would like to give qualitative explanation on the basic principles of Deep Level Transient Spectroscopy (DLTS). For details, see *e.g.* ref. [4]. We consider modification to effective capacitance (6.24), which depends on the reverse bias voltage V. Let  $N_D$  be the shallow donor concentration,  $N_P$  the one for a deep donor. In the region where this deep donor responds to change in the bias voltage, the voltage-differential capacitance is expressed as a function of reverse voltage V as

$$w_d(V) \approx \left[\frac{2\epsilon\epsilon_0(V+V_{\rm bi})}{e(N_{\rm D}+N_{\rm P})}\right]^{1/2} \approx w_n,\tag{6B.1}$$

$$C(V) = \sqrt{\frac{\epsilon\epsilon_0 e(N_{\rm D} + N_{\rm P})}{2}} (V + V_{\rm bi})^{-1/2}.$$

(6B.2)

For simplicity, we consider the situation that the reverse bias  $V_p$  is applied and kept for sufficiently long time for electrons to escape from the depletion layer including the deep levels \*<sup>2</sup>. Now V is abruptly lowered to  $V_0 < V_p$  and the carriers are captured by the donor levels within  $w(V_0) < x \le w(V_p)$ . Shallow donors have high capture rate and can respond within ms without delay, deep levels, on the other hand, the capture rate strongly depends on temperature and with decreasing temperature, the average time for capture often elongates from ms to s, min, hour and sometimes day. Then if we open up a fixed time window and observe the time evolution of C, the time dependence is observed in the time window at some temperature range and in low or high temperature regions the effect of deep levels does not observed.

Such a process is illustrated in Fig. 6B.1(a). We take t = 0 at the time the reverse bias is changed:  $V_p \rightarrow V_0$  and measure the difference in the differential capacitances at  $t_1$  and  $t_2$ :  $\Delta C = |C(t_1) - C(t_2)|$  as a function of temperature T.

We now assume existence of two species of deep donors, which have temperature dependent capture cross sections shown in the upper panel of Fig. 6B.1(b).  $\Delta C$  should show two peaks in the temperature dependence. Analysis of the data gives the concentration and capture cross section of each deep level, and combination with photo-response, in some

<sup>\*&</sup>lt;sup>2</sup> At low temperatures the capture/emission rates of deep levels become very small and it is not rare that we need days for the emission. So this condition is, in general, hard to be fulfilled. But the consideration of this does not give significant change and thus we adopt the assumption.

Fig. 6B.1 (a) Upper panel: Illustration that the change in the reverse bias  $V_p \rightarrow V_0$  makes shallow levels and a part of deep levels ready for catching carriers. Lower panel: With progress in capture of carriers, differential capacitance C(V) shows transient response. (b) Upper panel: two deep levels exist and assumed temperature dependences of the capture cross section  $\sigma$  are illustrated. Lower panel: shows how the DLTS signal appears from the temperature dependence  $\sigma(T)$ .

cases identification of deep levels or at least energy positions can be measured[4]. With variation of  $V_0$  and  $V_p$ , depth profile of deep levels can be obtained also.

### References

[1] 菊池誠「半導体の理論と応用(中)」(裳華房, 1963).

[2] 勝本信吾物性研究 電子版 Vol.3, No.3, 033209 (2014 年 8 月号)

http://mercury.yukawa.kyoto-u.ac.jp/~bussei.kenkyu/pdf/03/3/9999-033209.pdf

- [3] Jon Gertner, "The Idea Factory: Bell Labs and the Great Age of American Innovation", (Penguin Press, 2012).

- [4] 国府田隆夫, 柊元宏 「光物性測定技術」(東大出版会, 1983).

- [5] M. Jaros, "Deep levels in Semiconductors" (CRC Press, 1982).